Non si sale veloci celebrando i risultati quanto superando le disillusioni

MICROPROCESSORI E MICROCONTROLLORI

… studiare, studiare ed ancora studiare,

è il solo modo di capire quanto possa

essere grande sia la propria ignoranza!

I MICROCONTROLLORI 8051 E PIC16F84A

Il microcontrollore 8051 è uno dei single chip più diffusi.

Prodotto all’inizio degli anni 80 inizialmente dall’Intel, oggi è

implementato in centinaia di versioni anche da altri produttori.

Il micro è costituito dai seguenti componenti:

•

core a 8 bit ottimizzato per applicazioni di controllo;

•

Internal RAM da 128 byte dedicata ai dati;

•

Internal ROM da 4 Kbyte dedicati al programma;

•

External RAM:

– da 64 Kbyte indirizzabile per i dati;

– da 64 Kbyte indirizzabile per i programmi;

•

32 linee di I/O bidirezionali digitali indirizzabili separatamente;

•

2 timer/contatori a 16 bit;

•

porta seriale full-duplex;

•

5 linee di interrupt di cui 2 esterne, ciascuna con 2 livelli

di priorità;

•

generatore di clock interno;

•

eventuali convertitori ADC e DAC implementati da alcuni

costruttori, conservando però la compatibilità.

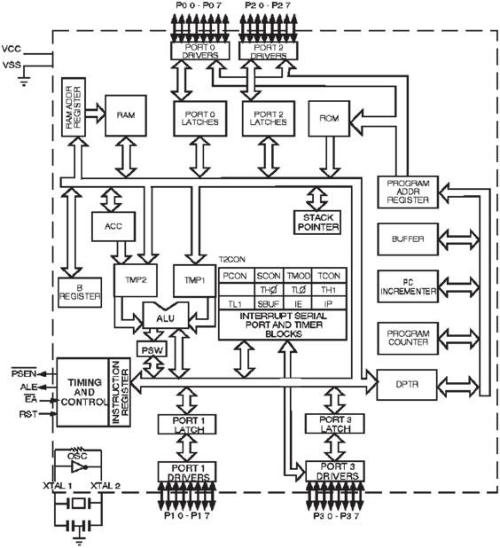

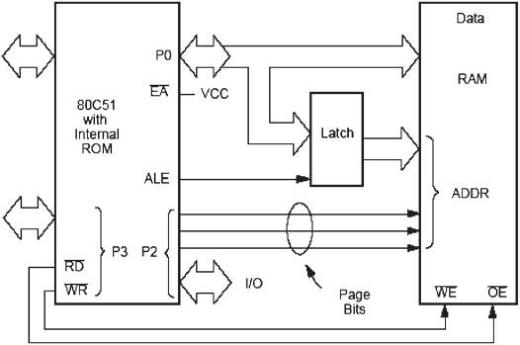

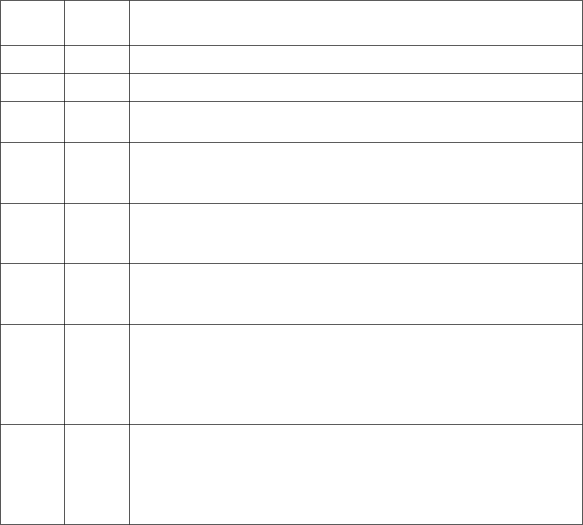

Nella sottostante figura è illustrata la connessione tra il core e i componenti accessori.

Schema a blocchi del microcontrollore 80C51

Architettura interna del microcontrollore 80C51 ed il suo Pin-Out

Architettura interna

L’architettura interna dell’8051 (sopre raffigurata) è di tipo Harvard con spazio e bus

separati per dati e programma.

La memoria è di tre tipi:

•

memoria interna (On-Chip);

•

memoria esterna di programma

(External Code);

•

memoria esterna di dati (External RAM).

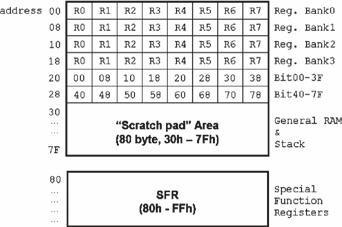

La memoria interna si compone di 2 parti (vedi figura

a lato):

•

RAM interna che a sua volta si divide in:

– un banco di registri 0 (00H-07H) e i banchi 1, 2

e 3 (08H-1FH) che possono essere utilizzati tramite

SFR;

– una memoria a bit (20H-2FH);

– memoria utente e area stack, 80 byte (30H-7FH)

memoria SFR (Special Function Registers).

Se si accede alla memoria con il metodo dell’indirizzamento diretto, nel codice

dell’istruzione è necessario specificare gli indirizzi:

•

da 00H a 7FH per la memoria interna;

•

da 80H a FFH per gli SFR

I registri

I registri sono utilizzati come memoria temporanea e per trasferire dati da una locazione di

memoria ad un’altra.

Il banco di registri 0 viene richiamato nelle istruzioni per default.

Infatti ADD A, R4 somma il contenuto del registro R4 del banco 0, quindi con indirizzo 04H,

con l’accumulatore e pone il risultato nell’accumulatore stesso.

Se si desidera utilizzare il registro R4 di un altro banco (ad esempio il primo) è necessario

specificare nell’istruzione l’indirizzo relativo, in questo caso 0CH): ADD A,0C.

La memoria a bit (bit mapped), alla quale si accede con gli indirizzi da 20H a 2FH, è

gestibile bit a bit con istruzioni particolari quali SETB e CLR.

Esempio

Scrivere le istruzioni per settare il bit 25H e resettare il bit 26H.

Per settare il bit 25H il comando è SETB 25.

Per resettare il bit 26H il comando è: CLR 26.

La memoria (utente e stack) è utilizzata sia per memorizzare in modo veloce e frequente

le variabili del codice utente sia per l’area stack.

Questa memoria conta soli 80 byte quindi la parte riservata per lo stack è limitata.

I registri speciali (SFR), indirizzati in modo diretto così che è sempre possibile prelevare

il giusto dato, servono per le seguenti funzioni:

•

accesso per lettura e scrittura sulla porta seriale e relativa impostazione del baud rate;

•

accesso alle linee di I/O;

•

accesso ai due timer;

•

configurazione degli interrupt.

L’area dei registri SFR non può essere utilizzata come RAM addizionale, salvo eccezioni.

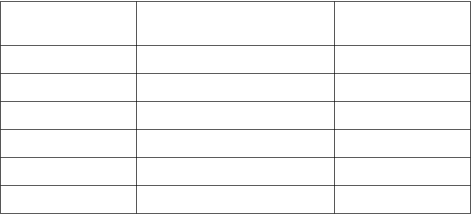

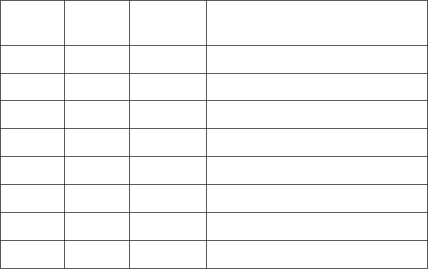

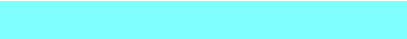

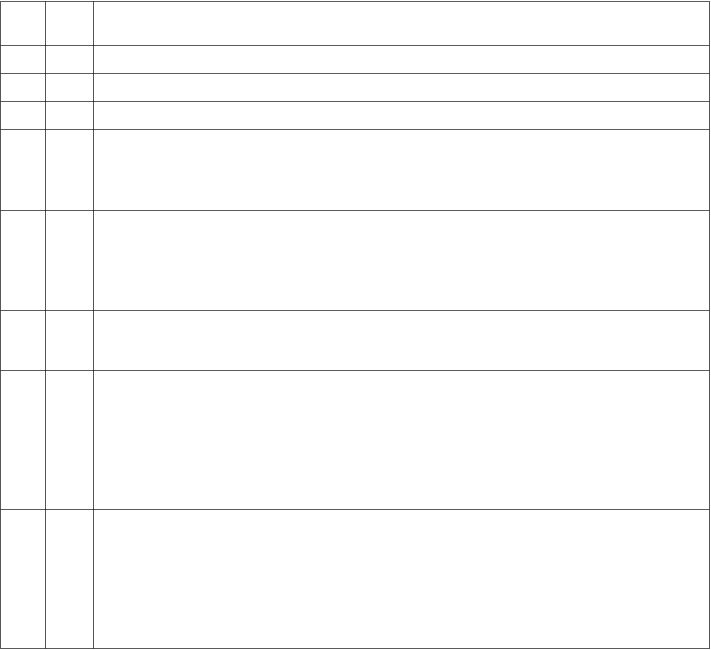

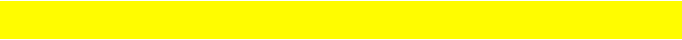

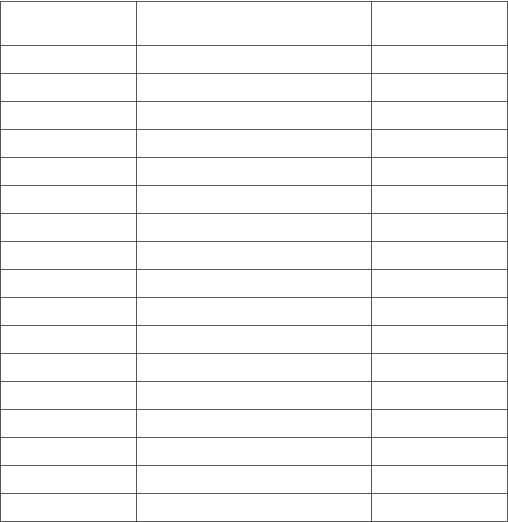

I registri SFR possono esser suddivisi in 3 categorie (vedi la sottostante tabella):

– per task generici (A, B, DPTR, PC, SP, SBUF, TL0/TH0, TL1/TH1);

– di controllo (PSW, PCON, TCON, TMOD, SCON, IE, IP);

– per le porte di I/O (P0, P1, P2, P3).

L’accumulatore, indicato con A nelle istruzioni, è un registro a 8 bit individuato dall’indirizzo

E0H.

È utilizzato dalla metà delle 255 istruzioni.

Il registro B, appartenente agli SFR, è un registro a 8 bit residente all’indirizzo F0H.

È usato dalle istruzioni:

• MUL AB;

• DIV AB;

Banco di registri SFR.

Indirizzi

Registri

Indirizzi

80

PO

SP

DPL

DPH

PCON

87

88

TCON

TMOD

TLO

TL1

TH0

TH1

8F

90

P1

97

98

SCON

SBUF

9F

A0

P2

A7

A8

IE

AF

B0

P3

B7

B8

IP

BF

C0

C7

C8

CF

D0

PSW

D7

D8

DF

E0

Acc

E7

E8

EF

F0

B

F7

F8

FF

per contenere il secondo operando nelle operazioni di moltiplicazione e divisione e

come nono registro associato al banco dei registri R.

Il registro DPTR (Data PoinTer Register) è un puntatore dati, quindi ha un formato a 16 bit.

È ottenuto da due registri a 8 bit DPL e DPH con indirizzi rispettivamente 82H e 83H.

Può essere utilizzato dal codice per memorizzare dati a 2 byte.

Il registro PC (Program Counter) è a 16 bit.

Al bootstrap è inizializzato con 0000H.

Il PC non è accessibile direttamente dal codice.

Il registro SP (Stack Pointer) è a 8 bit quindi può indirizzare un’area stack da 256 byte.

È residente all’indirizzo 81H e il suo contenuto in fase di inizializzazione è 07H.

Il suo contenuto viene modificato con le istruzioni PUSH, POP, ACALL, LCALL, RET, RETI e

da tutte le operazioni di interrupt.

Il registro SBUF (Serial BUFfer), residente all’indirizzo 99H, è usato per inviare e ricevere i

dati dalla porta seriale.

Se si scrive un dato nel registro SBUF, questo viene inviato sulla porta seriale dal pin TXD.

Analogamente ogni dato ricevuto dalla seriale attraverso il pin RXD viene reso disponibile al

programma utente mediante una lettura nel registro SBUF.

I registri TL0/TH0, entrambi a 8 bit e quindi in modo congiunto a 16 bit, residenti agli

indirizzi 8AH/8BH, contengono lo stato del timer 0 che è configurato da TMOD.

Generalmente i timer funzionano sempre in modo ascendente.

I registri TL1/TH1, entrambi a 8 bit e quindi in modo congiunto a 16 bit, residenti agli

indirizzi 8AH/8BH, contengono lo stato del timer 1 che è configurato da TMOD.

Generalmente i timer funzionano sempre in modo ascendente.

Il registro PSW (Program Status Word), indirizzo D0H e indirizzabile a bit, contiene:

•

CY (PSW.7) CarrY flag;

•

• AC (PSW.6) Auxiliary Carry;

•

F0 (PSW.5) Flag utilizzabile dall’utente;

•

RS1 (PSW.4) bit 1 di selezione del banco di registri;

•

RS0 (PSW.3) bit 0 di selezione del banco di registri, insieme a RS1 seleziona il banco di

registri R secondo la sotostante tavola Selezione dei Registri RS

•

OV (PSW.2) OVerflow;

•

- (PSW.1) flag definibile dall’utente;

•

P (PSW.0) Parity flag, flag di parità pari.

Il registro PCON (Power CONtrol), indirizzo 87H, è utilizzato per:

•

controllare il power mode del micro;

•

consentire il passaggio nello stato sleep che richiede minore potenza;

•

permettere, con il set di un bit, di raddoppiare il baud rate effettivo della porta seriale.

Il registro TCON (Timer CONtrol), indirizzo 88H e indirizzabile a bit, serve a:

•

configurare e modificare il funzionamento dei timer;

•

indicare con un bit l’overflow del timer;

•

configurare gli interrupt esterni;

•

segnalare l’attivazione di un interrupt esterno.

Il registro TMOD (Timer MODe), indirizzo 89H, serve a programmare il funzionamento dei

2 timer come:

•

2 timer separati;

•

un unico timer da 16 bit;

•

un unico timer da 13 bit;

•

un timer a 8 bit con autocaricamento;

•

un timer come contatore se è attivato un bit dall’esterno;

•

un timer come contatore di eventi se è attivato un bit dall’esterno.

Il registro SCON (Serial Control), indirizzabile a bit all’indirizzo 98H, serve a configurare il

funzionamento della porta seriale, ne abilita la ricezione e programma il baud rate.

Alcuni flag segnalano l’avvenuta ricezione o trasmissione con successo del dato.

Il registro IE (Interrupt Enable), indirizzo A8H, serve ad abilitare e disabilitare gli interrupt.

Il bit più significativo, che è prioritario rispetto a tutti gli altri bit, abilita e disabilita tutti i

segnali di interrupt.

I 7 bit meno significativi abitano e disabilitano gli interrupt individualmente.

Il registro IP (Interrupt Priority), indirizzo B8H, è un registro che consente di stabilire

la priorità tra gli interrupt.

Un interrupt con priorità più bassa (0) non può interrompere un interrupt con priorità

più elevata (1).

P0 (porta 0), P1 (porta 1), P2 (porta 2) e P3 (porta 3) con indirizzi rispettivamente 80H,

90H, A0H e B0H, sono porte a 8 bit di input/output.

Ciascun bit di ogni porta corrisponde a un pin dell’integrato.

I pin della P0 vanno da P0.0 a P0.7 e così per le altre porte.

Ogni pin può essere forzato a livello alto o basso.

Se il micro ha una memoria esterna, P0 e P2 sono adibite esclusivamente alla gestione

degli indirizzi della memoria.

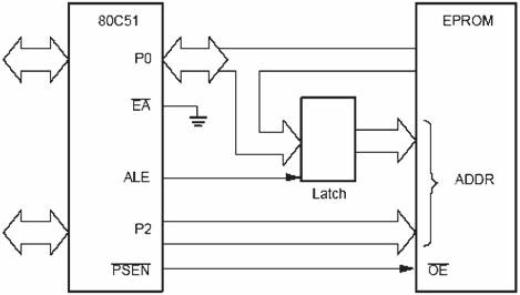

Memoria esterna di programma

La memoria esterna è di solito ROM, EPROM o FLASH e contiene il programma utente da

eseguire.

Sono possibili due soluzioni:

•

EA = 1, la memoria programma è formata da 4 KB interni e i restanti 60 KB esterni;

•

EA = 0, la memoria programma 64 KB è tutta esterna.

Nella sottostante figura è riportato lo schema di interfacciamento tra il micro e una EPROM.

I segnali per la gestione dell’interfacciamento sono i seguenti:

• P2.0-P2.7 è la parte alta dell’indirizzo;

• la porta P0 trasmette la parte bassa dell’indirizzo al

Latch per essere libera di ricevere il dato dalla EPROM;

• P0.0-P0.7 è la parte bassa dell’indirizzo;

• P0.0-P0.7 è il dato trasmesso dalla EPROM al micro;

• PSEN abilita la EPROM alla trasmissione del dato.

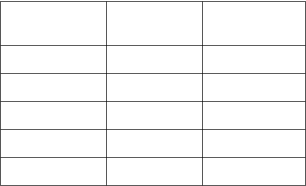

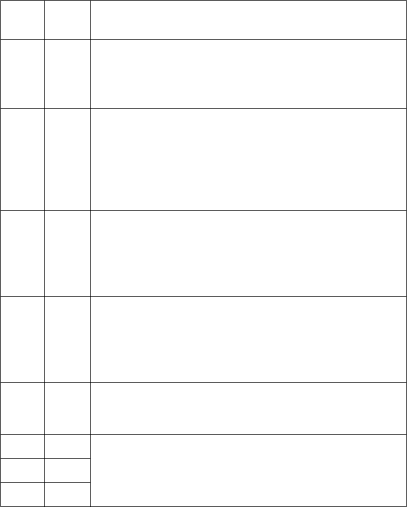

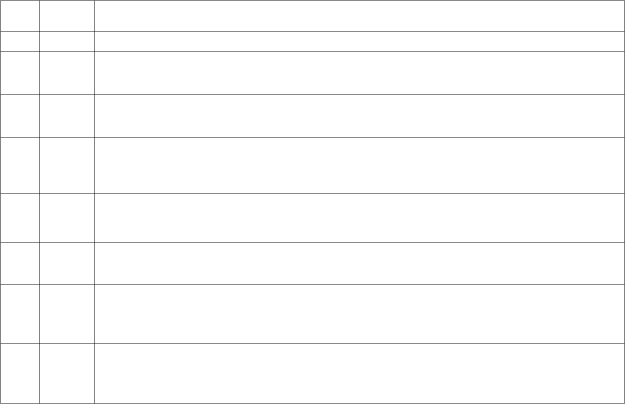

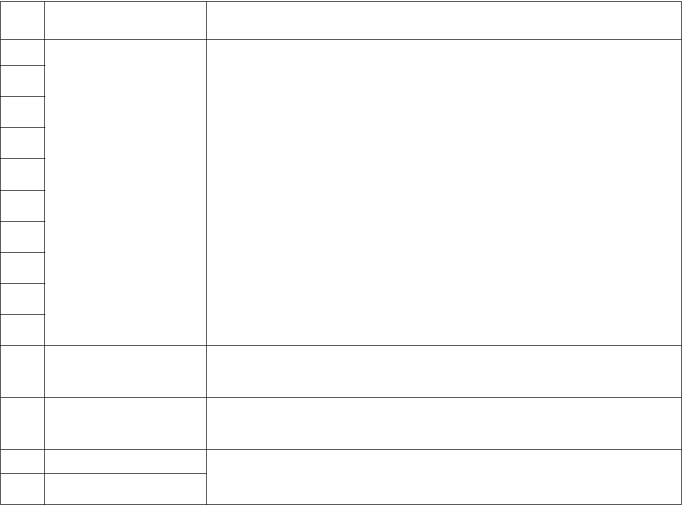

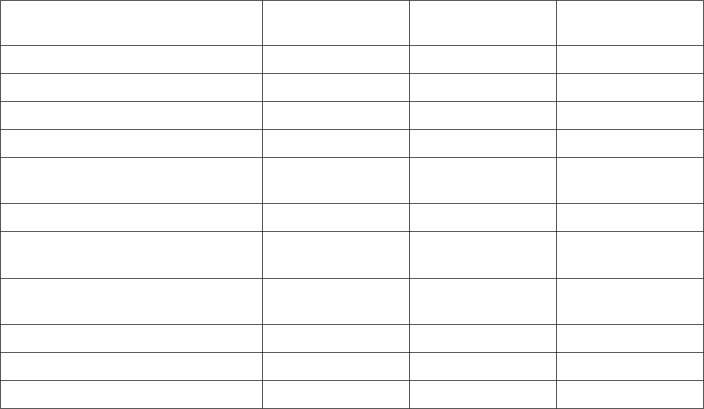

Selezione dei registri RS.

RS1

RS0

Banco di registri R

Indirizzi

0

0

0

00H-07H

0

1

1

08H-0FH

1

0

2

10H-17H

1

1

3

18H-1FH

RAM esterna

La RAM esterna, normalmente statica o FLASH, può avere una dimensione massima di

64 KB, mentre la RAM interna è di 128 byte.

La RAM interna è più veloce mentre quella esterna è molto più lenta.

Ad esempio incrementare una variabile interna necessita di un ciclo di istruzione mentre la

stessa operazione nella memoria esterna necessita di 7 cicli di istruzione.

Nella sottostante figura è riportato lo schema di interfacciamento tra il micro e la

RAM esterna.

I segnali per la gestione dell’interfacciamento sono i seguenti:

• P2.0-P2.7 è la parte alta dell’indirizzo;

• la porta P0 trasmette la parte bassa dell’indirizzo al

Latch per essere libera di ricevere il dato dalla EPROM;

• P0.0-P0.7 è la parte bassa dell’indirizzo;

• P0.0-P0.7 è il dato trasmesso dalla EPROM al micro

Interfacciamento del microcontrollore 80C51 con una EPROM

Interfacciamento del microcontrollore 80C51con una RAM

• P3.6 abilitazione alla scrittura;

• P3.7 abilitazione alla lettura.

Modalità di indirizzamento

Le modalità di indirizzamento sono le seguenti:

• indirizzamento immediato;

• indirizzamento diretto;

• indirizzamento indiretto;

• esterno diretto;

• esterno indiretto.

Indirizzamento immediato.

In questo modo di indirizzamento l’operando è dato immediatamente nel codice operativo

dell’istruzione.

Il dato è una costante e non può essere un indirizzo.

Il metodo è veloce ma non ha alcuna flessibilità (hard-coded).

Esempio

MOV A,#30H

;nell’accumulatore viene caricato il dato esadecimale 30

Indirizzamento diretto.

Nell’istruzione viene specificato l’indirizzo di memoria dove si trova l’operando.

È un metodo valido solo per la memoria interna.

Se l’operando si trova nella memoria esterna si deve usare l’indirizzamento indiretto.

L’indirizzamento è flessibile e veloce poiché il dato è comunque nella memoria interna.

Esempio

MOV A,10H

;l’accumulatore A è caricato con il contenuto della locazione di memoria

;il cui indirizzo è 10H

Indirizzamento indiretto.

Nell’istruzione viene indicato il registro nel quale si trova l’indirizzo di memoria dove

prelevare l’operando.

Il metodo è estremamente flessibile poiché consente di prelevare un operando sia dalla

memoria interna sia da quella esterna.

Non è possibile utilizzare questo metodo per prelevare dati da SFR, non è utilizzabile per

scrivere in una porta seriale.

I registri contenenti gli indirizzi a 8 bit possono essere R0 e R1 mentre l’unico registro che

può contenere un indirizzo a 16 bit è il DPTR.

Esempio

MOV A, @R0

;nell’accumulatore viene caricato il dato presente in memoria all’indirizzo

;contenuto nel registro R0

Indirizzamento esterno diretto.

È il modo di indirizzamento per caricare la memoria esterna.

Sono solo due le istruzioni che utilizzano questo metodo:

MOVA A, DPTR

MOVX @DPTR,A

Nella prima istruzione il dato che si trova in memoria all’indirizzo specificato dal registro

DPTR deve essere memorizzato nell’accumulatore.

Nella seconda istruzione il contenuto dell’accumulatore viene caricato in memoria all’indirizzo

contenuto dal registro DPTR.

Indirizzamento esterno indiretto.

È un modo usato per indirizzare la memoria esterna.

Esempio

MOV @R0, A

Il dato presente nell’accumulatore viene inviato in memoria all’indirizzo contenuto in R0.

Poiché R0 è un registro a 8 bit, è possibile indirizzare solo 256 byte della memoria esterna.

Indirizzamento implicito.

Nell’istruzione sono specificati i registri ai quali si farà l’accesso.

Esempio

DIV AB

Porta seriale

La porta seriale consente la comunicazione full duplex.

Il dato da trasmettere o da ricevere viene posto nel registro SBUF.

La segnalazione dell’avvenuta ricezione o trasmissione corretta dell’informazione è segnalata

dallo stesso registro.

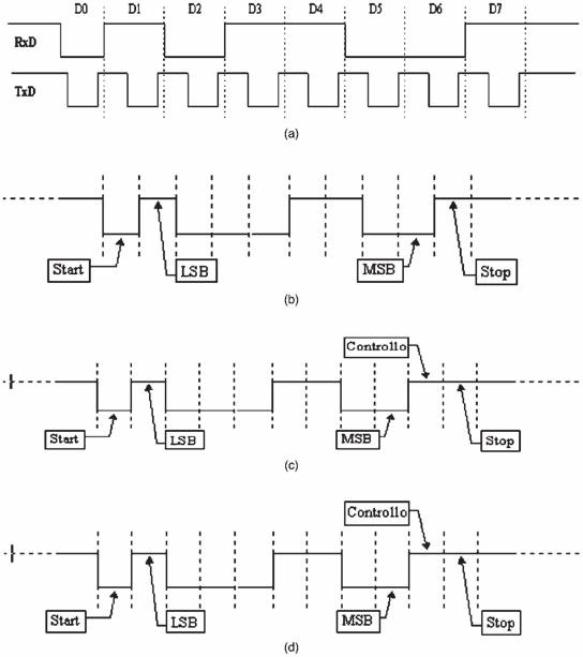

Nelle soprastanti tabelle sono riportate le configurazioni della porta seriale, che può operare

in 4 modi:

•

modo 0; i dati a 8 bit sono trasferiti in modo seriale tramite il pin RXD.

Da TXD viene emesso il clock generato dal registro a scorrimento; la velocità in baud è

1/12 della frequenza dell’oscillatore;

nella sottostante figura (a) è illustrato il diagramma temporale;

•

modo 1; è una comunicazione a 10 bit (bit di start + 8 bit del dato + bit di stop)

(figura b); la trasmissione avviene su TXD e la ricezione su RXD; in ricezione il bit di

stop è scritto su RB8 nel registro SCON; la velocità è variabile;

•

modo 2; è una comunicazione a 11 bit (un bit di start+8 bit di dato+un bit programma-

-bile dall’utente+un bit di stop); in figura ( c) vi è il diagramma temporale; la velocità è

programmabile a 1/32 o 1/64 della frequenza di oscillazione;

•

modo 3; come il modo 2 ma la velocità è data dal timer 1 (figura d)

SM0

Bit di modo 0 (NOTE 0)

SM1

Bit di modo 1 (NOTE 1)

SM2

Abilita la comunicazione multiprocessore in modo 2 e 3

REN

Set/Cleared via software per ricezione abilitata/disabilitata

TB8

Nono bit che sarà trasmesso in modo 2 e 3 - Set/Cleared via software

RB8

Nono bit che è stato ricevuto in modo 2 e 3

In modo 1 se SM2=0, RB8 è il bit di stop ricevuto

In modo 0 RB8 non è usato

TI

Flag di interrupt in trasmissione

Settato via hardware quando è stato trasmesso l’8º bit in modo 0 o all’inizio del bit di stop

negli altri modi

Deve essere cancellato via software

RI

Flag di interrupt in ricezione

Settato via hardware alla fine dell’8º bit in modo 0 o a metà del bit di stop negli altri modi

Deve essere settato via software

Registro SCON per la programmazione della porta seriale.

SM0

SM1

Mode

Description

Baud rate

0

0

0

Shift Register

Fosc/12

0

1

1

8-bit UART

Variable

1

0

2

9-bit UART

Fosc/64 or Fosc/32

1

1

3

9-bit UART

Variable

I timer/contatori

Il micro 8051 è dotato di 2 registri timer/contatori a 16 bit che svolgono le seguenti funzioni:

•

conteggiare il tempo tra due eventi

Funzionamento della porta seriale: in modo 0 (a), in modo 1 (b), in modo 2 (c), in modo 3 (d)

•

contare il numero di eventi;

•

generare il baud rate per la porta seriale.

Nel funzionamento come timer, il registro è incrementato a ogni ciclo macchina.

Poiché ogni ciclo macchina è formato da dodici colpi di clock, il conteggio progredisce ogni

dodicesimo impulso del clock.

Nel funzionamento come contaeventi, il registro viene incrementato ogni transizione

da 1 a 0 dell’ingresso T0 e T1.

La massima frequenza è 1/24 della frequenza di clock.

Nella sottostante tabella è riportata la configurazione e l’inizializzazione dei timer

Configurazione e inizializzazione dei timer.

SFR

Descrizione

Indirizzo SFR

TMOD

Timer Mode

89H

TCON

Timer Control

88H

TH1

Timer 1 byte basso

8BH

TH1

Timer 1 byte alto

8DH

TL0

Timer 0 byte basso

8AH

TH0

Timer 0 byte alto

8CH

Gli interrupt

Il micro 8051 è dotato di 5 sorgenti di interrupt:

• interrupt esterno 0;

• interrupt esterno 1;

• ricezione/trasmissione seriale;

• overflow timer 0;

• overflow timer 1.

Se sono stati abilitati gli interrupt, il micro sospende l’esecuzione del programma

principale ed esegue l’interrupt handler (subroutine) del dispositivo che ha richiesto

l’intervento.

Ogni sorgente di interruzione può essere programmata individualmente ad uno di due livelli

di priorità (alta o bassa) settando o azzerando un bit nel registro IP (SFR).

Se due interrupt dello stesso livello si presentano contemporaneamente, il micro esegue

una sequenza di polling assegnando la priorità

indicata nella tabella a lato.

Gli interrupt sono inizialmente tutti disabilitati.

Pertanto è compito del programmatore configurare

il registro IE (SFR), come nella sottostante tabella.

Priorità interna agli stessi livelli

Priority

Within level

Source

Address

Highest

IE0

0003H

TF0

000BH

IE1

0013H

TF1

001BH

Lowest

RI+TI

0023H

Configurazion del registro IE

Bit

Symbol

Address

Function

IE.7

EA

AFH

Disabilita tutti gli interrupt

IE.6

--

AEH

Reserved

IE.5

--

ADH

Reserved

IE.4

ES

ACH

Abilita interrupt seriale

IE.3

ET1

ABH

Abilita interrupt timer 1

IE.2

EX1

AAH

Abilita interrupt esterno INT1

IE.1

ET0

A9H

Abilita interrupt timer 0

IE.0

EX0

A8H

Abilita interrupt esterno INT0

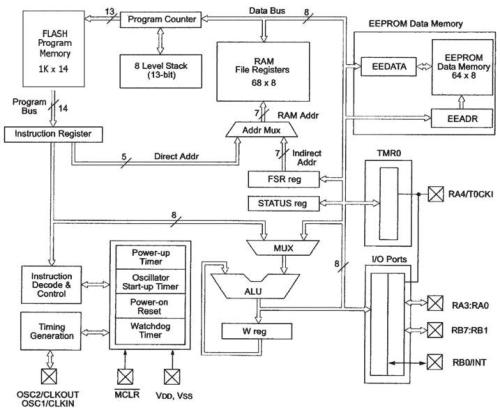

Il microcontrollore PIC 16F84A

L’architettura dei microcontrollori PIC (Peripherical Interface Controller) della Microchip si

basa su una CPU di tipo RISC, con separazione tra bus dati e bus istruzioni, quindi con

un’architettura di tipo Harvard.

Per quasi tutti i modelli di PIC l’unica area RAM utilizzabile è di fatto l’elevato numero di

registri interni, non avendo alcuna possibilità di indirizzare una memoria esterna.

Il PIC16F84A, del quale, a lato

lo schema a blocchi, ha una

RAM interna con una dimen-

-sione da 512 a 2024 parole

di istruzioni.

La RAM interna, vista come un

insieme di registri a 8 bit, è

costituita da 80 fino a 248

registri, a seconda del modello

di PIC.

Oltre ai registri generali il

micro, con periferiche interne,

è dotato anche di registri

specializzati nei modelli.

La disponibilità di molti registri

rende molto veloce l’elabora-

-zione delle istruzioni e le

risposte alle interruzioni, ma

l’area stack è piuttosto ridotta,

da 2 a 16 livelli.

L’impossibilità di gestire una memoria esterna non limita la lunghezza del programma dato

che il codice macchina è piuttosto compatto, infatti il formato delle istruzioni va da 12 a

16 bit.

Il modello 17C42 è in grado di gestire una memoria esterna e quindi costituisce un’eccezione

della famiglia PIC.

La CPU interna,che può essere a 8 o a 16 bit, è semplice e molto veloce in quanto esegue le

istruzioni in un ciclo macchina.

I PIC non hanno la necessità di un clock molto elevato poiché le istruzioni sono semplici e

vengono eseguite molto velocemente.

La frequenza si aggira sui 4-8 MHz nelle versioni base, fino a 33-50 MHz nelle versioni di

fascia alta.

L’architettura Harvard ha un bus dati a 8 bit e un bus indirizzi a 12 o a 16 bit.

La programmazione si presenta abbastanza semplice sia per il limitato numero di istruzioni,

in genere non oltre 35, sia per la ortogonalità dei registri.

Le istruzioni aritmetiche e logiche possono avere come operandi due registri qualunque.

Con una modalità di indirizzamento indiretto vi è la possibilità di spostare i dati dalla

memoria programma alla memoria dati.

Nei modelli base non vi sono ingressi per gli interrupt, mentre nei modelli di fascia media e

alta ve ne sono diversi e alcuni anche collegati direttamente alle periferiche interne, come

per esempio il timer.

Il timer è sempre presente in tutte le versioni, le altre periferiche, quali il convertitore AD,

il PWM e la porta seriale, sono disponibili in alcuni modelli.

I PIC sono disponibili nelle versioni a basso consumo e con tensione di alimentazione ridotta

(2 V).

In generale i PIC sono componenti OTP ma vi sono anche alcune versioni che hanno una

EEPROM interna.

In base alla CPU si possono distinguere in micro a:

• 8 bit (serie PIC12, PIC16, PIC17, PIC18);

• 16 bit (serie PIC24 e PIC33).

Il PIC16F84A ha due caratteristiche importanti:

• l’abbondanza di registri;

• la presenza di porte di I/O in grado di pilotare carichi esterni.

Le periferiche di un PIC sono:

•

porte; sono le periferiche di base per comunicare da e verso l’esterno; devono essere

configurate dall’utente come uscite o ingressi;

•

memoria; normalmente di tipo FLASH, locazione dove vengono conservati i dati e il

programma anche in assenza di alimentazione;

•

ADC; è il convertitore che consente di trasformare un segnale d’ingresso analogico in

uno digitale a 10 bit;

•

timer; sono presenti in tutte le versioni dei PIC e servono per misurare intervalli di tempo

o contare eventi esterni;

• PWM; serve a generare un segnale di comando digitale di tipo PWM;

• comunicazioni; è la via di collegamento con protocolli standard con altri componenti.

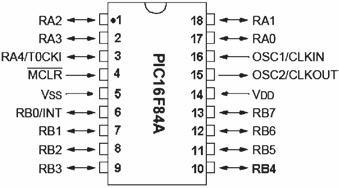

Schema a blocchi e piedinatura

Il PIC16F84 è un micro a 8 bit e ha a disposizione 35 istruzioni tutte eseguite in un ciclo

tranne quelle di branch che necessitano di 2 cicli.

I modi di indirizzamento sono diretto, indiretto e relativo.

Il clock ha una frequenza di 20 MHz e ogni ciclo di istruzione dura 200 ns.

Tutti i registri sono a 8 bit e la memoria è organizzata in byte.

Le caratteristiche hardware del PIC16F84 sono le seguenti:

•

CPU a 8 bit;

•

memoria:

– FLASH 1 K × 14 bit per il codice;

– RAM da 68 byte per le variabili;

– 15 registri speciali;

– EEPROM da 64 byte per dati di configurazione e taratura;

– area stack a 8 livelli;13 pin di I/O ad alta corrente;

•

4 sorgenti di interrupt;

•

timer a 8 bit;

•

watchdog timer a 8 bit;

•

prescaler programmabile per i 2 timer;

•

modalità standby;

•

programmabilità in-circuit;

•

alimentazione da 2 V a 6 V;

•

clock massimo a 10 MHz.

In figura a lato è riportata la piedinatura e nella

sottostante tabella la descrizione delle funzioni dei pin.

Descrizione della funzione dei pin del PIC16F84A

Nome Pin

Pin

Type

I/O/P

Descrizione

OSC1/CLKIN

16

I

Può essere collegato a un circuito esterno (quarzo o rete RC) o essere

utilizzato per ricevere un segnale da un oscillatore esterno (CLKIN)

OSC2/CLKOUT

15

o

Può essere collegato a un circuito esterno (quarzo o rete RC) o essere

utilizzato per generare all’esterno il clock interno

MCLR

4

I/P

Master clear per un reset hardware del micro

RA0

RA1

RA2

RA3

RA4/T0CKI

17

18

1

2

3

I/O

I/O

I/O

I/O

I/O

Porta bidirezionale a 5 bit

Può essere utilizzato come bit di I/O del Port A o come ingresso per il

registro TMR0

Port B bidirezionale a 8 bit

Può essere programmato per un weak pull-up interno su tutti gli ingressi

Svolge la doppia funzione: pin di I/O e interrupt dall’esterno

RB0/INT

RB1

RB2

RB3

RB4

RB5

RB6

RB75

6

7

8

9

10

11

12

13

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Una commutazione del segnale può svolgere la funzione di interrupt

Una commutazione del segnale può svolgere la funzione di interrupt

Usato in programmazione come DATA

Una commutazione del segnale può svolgere la funzione di interrupt

Usato in programmazione come CLOCK

Vss

5

P

Massa

VDD

14

P

Alimentazione

L’organizzazione della memoria

La memoria è divisa in blocco programma e blocco dati, ciascuno con il proprio bus.

È possibile quindi accedere a ogni blocco durante lo stesso ciclo di clock.

La memoria dati è composta da:

•

una RAM di uso generale;

•

dai registri SFR (Special Function Registers) usati per

controllare le operazioni della CPU e i moduli periferici.

•

da una EEPROM da 64 byte non indirizzabile diret-

-tamente ma mappata in modo indiretto.

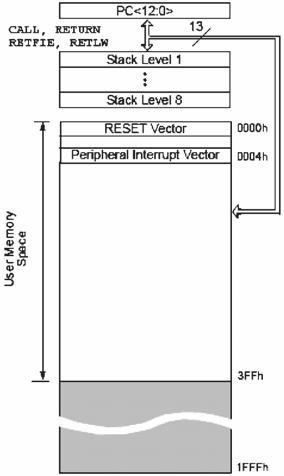

Il blocco codice (vedi figura a lato) è costituito da:

•

una RAM che funge da area stack;

•

una EEPROM per il programma.

Il PC, con dimensione da 13 bit, è in grado di indirizzare

un banco di memoria da 8 KB × 14 ma ne può gestire

solo le prime 1024 locazioni (da 000H a 03FFH).

Tutte le altre locazioni sono rimappate su quelle dista-

-nti 1 KB.

In pratica per le locazioni 000H, 400H, 800H, 1000H,

ecc. l’istruzione sarà sempre la stessa.

Tra tutte le locazioni di memoria, due sono particola-

-rmente importanti:

•

la locazione 0000H perché è la cella da cui ha inizio

l’esecuzione del programma o il microcontrollore

riparte dopo un reset;

•

la locazione 0004H perché da questa cella ha inizio

l’esecuzione della subroutine di servizio degli inter-

-rupt; se non viene utilizzata la modalità

interrupt, la locazione può essere usata

come una qualsiasi locazione di memoria

per il programma.

La memoria dati è composta di due parti:

•

SFR (Special Function Registers) che control-

-lano le periferiche;

•

GPR (General Purpose RAM).

La suddivisione della memoria in banchi richiede per la selezione del banco l’uso di

bit di controllo residenti nello STATUS register.

Nella figura a lato è illustrata la mappa della

memoria dati.

Con le istruzioni MOVWF e MOVF è possibile

trasferire i dati dall’accumulatore (W) alla RAM

(F) e viceversa.

Mappa della memoria programmata

SFR (Special Function Registers)

Gli SFR sono utilizzati dalla CPU e dalle funzioni

periferiche per controllare il funzionamento del

dispositivo.

Gli SFR possono essere classificati in due tipi:

•

core

•

periferici.

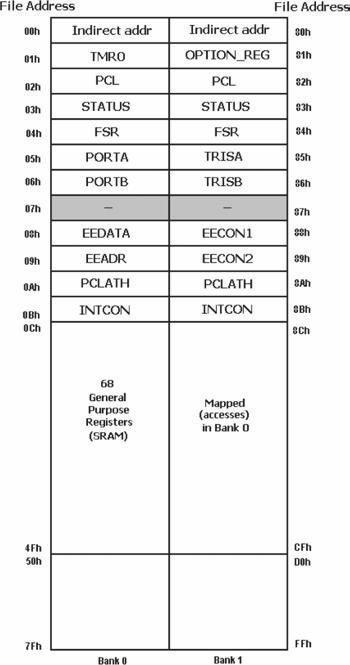

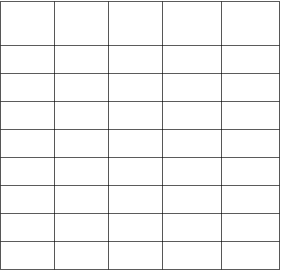

Nella sottostante tabella è riportata l’organiz-

-zazione dei registri SFR.

Organizzazione dei registri SFR.

Bank

Indirizzo

Simbolo

Bit dei registri

7

6

5

4

3

2

1

0

0

00h

INDF

Usa i contenuti di FSR per indirizzare la memoria dati (non è un registro fisico)

0

01h

TMR0

Clock/Counter da 8 bit in tempo reale

0

02h

PCL

8 bit di peso inferiore del PC

0

03h

STATUS

IRP

RP1

RP0

Z

DC

C

0

04h

FSR

Indirizzo indiretto della memoria dati del puntatore 0

0

05h

PORT A

--

--

--

T0CK1

RA3

RA2

RA1

RA0

0

06h

PORT B

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0

0

07h

--

Locazione non implementata, letta come 0

0

08h

EEDATA

Registro per dati EEPROM

0

09h

EEADR

Registro per indirizzi EEPROM

0

0Ah

PCLATH

--

--

--

Buffer di scrittura per i 5 bit superiori del PC

0

0Bh

INTCON

GIE

EEIE

T0IE

INTE

RBIE

T0IF

INTF

RBIF

1

80h

PCL

8 bit di peso inferiore del PC

1

83h

STATUS

IRP

RP1

RP0

Z

DC

C

1

84h

FSR

Indirizzo indiretto della memoria dati del puntatore 0

1

85h

TRIS A

--

--

--

Registro direzione dati del PORT A

1

86h

TRIS B

Registro direzione dati del PORT B

1

87h

Locazione non implementata, letta come 0

1

88h

EECON1

--

--

--

EEIF

WRERR

WREN

WR

RD

1

89h

EECON2

Registro 2 di controllo della EEPROM (non è un registro fisico)

1

0Ah

PCLATH

--

--

--

Buffer di scrittura per i 5 bit superiori del PC

1

0Bh

INTCON

GIE

EEIE

T0IE

INTE

RBE

T0IF

INTF

RBIF

L’accumulatore

Il microcontrollore è dotato anche di un registro (a 8 bit), non presente nei due banchi di

memoria perché è alla CPU, chiamato Work Register.

È identificato in alcune istruzioni come registro W.

Questo registro svolge le funzioni di accumulatore ed è anche utilizzato per svolgere varie e

altre funzioni.

Il PC (Program Counter)

Il Program Counter è un registro a 13 bit implementato in due coppie di registri del

register file:

•

registri PCL presenti nel Bank 0 all’indirizzo 02H e nel Bank 1 all’indirizzo 82H, questi

registri contengono la parte bassa del PC, ovvero i bit da 0 a 7;

•

registri PCLATH presenti nel Bank 0 all’indirizzo 0AH e nel Bank 1 all’indirizzo 8AH, questi

registri contengono i 5 bit di peso superiore, ovvero da 8 a 12.

Status Register

I registri Status hanno un formato da 8 bit e si trovano nel Bank 0 all’indirizzo 03H e nel

Bank 1 all’indirizzo 83H.

I bit dello Status servono come controllo delle operazioni aritmetiche, logiche e di alcune

istruzioni speciali.

Questi contengono i bit:

• dei risultati delle operazioni aritmetiche della ALU;

• del bit di selezione del banco della memoria dati;

• del bit dello stato di reset.

Nella sottostante tabella sono riportate le funzioni svolte dai bit del registro.

Come ogni registro, lo Status può essere il registro destinazione di qualunque istruzione.

Non tutte le istruzioni, aventi come destinazione lo Status, sono in grado di cambiare i bit.

Come indicato in tabella solo le istruzioni aritmetiche possono far variare il livello dei

bit Z, C e DC.

Per esempio dopo l’istruzione CLRF cambiano soltanto alcuni bit, infatti la situazione

dello Status diventa successivamente 000uu1uu (u = non cambiato).

Alcune istruzioni quali ad esempio BCF, BSF, SWAPF e MOVWF non cambiano nessun bit

dello Status (vedi tabella delle istruzioni).

Descrizione della funzione dei pin dello Status Register

Bit

Symbol

Function

7

IRP

Non utilizzato nel PIC16F84, rimane sempre a 0

6

RP1

Non utilizzato nel PIC16F84, rimane sempre a 0

5

RP0

RP0 = 0 seleziona il Bank 0

RP0 = 1 seleziona il Bank 1

4

Time Out

1 = dopo accensione, durante l’istruzione di CLRDT o SLEEP

0 = durante il time out del WDT

3

Power-down

1 = dopo l’accensione o l’operazione di CLRWDT

0 = dopo il passaggio in stand.by

2

Z

Zero

1 = se il risultato è 0

0 = se il risultato non è 0

1

DC

Digital Carry

Riporto/prestito nelle operazioni di somme (ADDLW e ADDWF)

e sottrazioni (SUBWF e SUBLW)

1 = riporto dal quarto bit

0 = nessun riporto

0

C

Carry

Riporto/prestito nelle operazioni di somme (ADDLW e ADDWF)

e sottrazioni (SUBWF e SUBLW)

1 = riporto dal bit più significativo

0 = nessun riporto

Option register

L’Option register presente nel Bank 1 all’indirizzo 81H serve a selezionare e abilitare

le funzioni del micro.

La descrizione delle funzioni svolte dai bit di questo registro sono riportate nelle due

sottostanti tabelle.

Descrizione dei bit dell’OPTION_REG.

Bit

Symbol

Description

7

RPBU

Bit di abilitazione dei pull-up del PORTB

1 = abilita

0 = disabilita

6

INTED

G

Bit di selezione del fronte di interrupt RB0/INT

1 = interrupt sul fronte di salita del pin RB0/INT

0 = interrupt sul fronte di discesa del pin RB0/INT

5

T0CS

Bit di selezione della sorgente del clock per TMR0

1 = abilita la sorgente di clock esterno su

RA4/T0CKI

0 = abilita la sorgente di clock interno

4

T0SE

Bit di selezione del fronte di commutazione del

segnale su RA4/

T0CKI

1 = commuta sulla transizione 1>0

0 = commuta sulla transizione 0>1

3

PSA

Assegna la gestione del prescaler

1 = prescaler assegnato a WDT

0 = prescaler assegnato TMR0

2

PS2

Bit he definicono il rapporto di prescaler

1

PS1

0

PS0

Descrizione dei rapporti di Prescaler

PS2

PS1

PS0

TMR0

WDT

0

0

0

1:2

1:1

0

0

1

1:4

1:2

0

1

0

1:8

1:4

0

1

1

1:16

1:8

1

0

0

1:32

1:16

1

0

1

1:64

1:32

1

1

0

1:128

1:64

1

1

1

1:256

1:128

Registri della EEPROM dati

La EEPROM dati non è indirizzabile direttamente ma è accessibile in modo indiretto

tramite i registri EEDATA e EEADR.

Il registro EEDATA, localizzato nel Bank 0 all’indirizzo 08H, è utilizzato dal micro per

contenere il dato letto dalla EEPROM ovvero per trasferire il dato nella EEPROM.

Il registro EEADR, situato nel Bank 0 all’indirizzo 09H, serve a memorizzare l’indirizzo della

EEPROM dove eseguire l’operazione di lettura o scrittura.

Tale registro pur avendo un formato da 8 bit e quindi potendo gestire una memoria da

256 byte, indirizza solo 64 byte poiché la restante parte della memoria non è disponibile in

questa versione di micro.

I registri EECON1 e EECON2, situati nel Bank 1 agli indirizzi rispettivamente 88H e 89H,

servono per controllare e avere informazioni sulle operazioni di lettura e scrittura nella

EEPROM.

Nella sottostante tabella sono illustrate le funzioni svolte dai pin del registro EECON1.

Il registro EECON2 funge da appoggio al registro EECON1 in fase di scrittura.

Infatti per scrivere un byte nella EEPROM dati è necessario preliminarmente scrivere in

sequenza 2 determinati valori (55H e AAH) in EECON2 e successivamente abilitare il

segnale di scrittura in EECON1.

Per l’operazione di lettura non è necessario il registro di appoggio EECON2.

Descrizione dei pin per la configurazione del registro EECON1.

Bit

Sym-

bol

Descrizione

7

--

Non implementato, letto come 0

6

--

Non implementato, letto come 0

5

--

Non implementato, letto come 0

4

EEIF

Flag di interrupt che segnala la fine dell’operazione di scrittura nella EEPROM

1 = fine scrittura

0 = scrittura non completata o non è iniziata

3

WRER

R

Flag di segnalazione di errore nella scrittura della EEPROM

1 = operazione di scrittura interrotto causa errore

0 = operazione di scrittura completato

2

WREN

Bit di abilitazione alla scrittura nella EEPROM

1 = abilitazione alla scrittura

0 = disabilitata la scrittura

1

WR

Bit di controllo del ciclo scrittura

1 = inizia il ciclo di scrittura

Il bit è azzerato via hardware una volta completata la scrittura deve essere settato via

software

0 = il ciclo di scrittura nella EEPROM è completato

0

RD

Bit di controllo del ciclo di lettura nella EEPROM

1 = inizia il ciclo di lettura, a fine operazione viene posto a 0 via hardware

Via software il bit può essere solo settato

0 = non inizia il ciclo di lettura

Esempio

Sequenza richiesta per l’inizio della scrittura nella EEPROM dati.

BSF STATUS, RP0

;Bank1

BCF INTCON, GIE

;disabilita interrupt

BSF EECON1, WREN

;abilita scrittura

MOVLW 55h ;

MOVWF EECON2

;scrive 55h

MOVLW AAh ;

MOVWF EECON2

;scrive AAh

BSF EECON1, WR

;setta il bit WR

;inizio scrittura

BSF INTCON, GIE

;abilita interrupt

Interrupt e INTCONT_REG

Nel PIC16F84 gli interrupt possono essere generati internamente o esternamente.

Gli interrupt possono essere generati da un dispositivo esterno:

• sul pin RB0/INT sul fronte di salita o su quello di discesa;

• quando vi è un cambiamento del segnale sui pin RB7-RB4.

Gli interrupt possono essere generati internamente:

•

da TMR0 al termine del conteggio;

•

al termine di un’operazione di scrittura nella EEPROM dati;

•

quando si verifica l’evento di wake-up from sleep ovvero quando il micro esce dallo

stato di power mode e diventa nuovamente operativo.

Il registro INTCONT, situato nel Bank 0 all’indirizzo 0BH e nel Bank 1 all’indirizzo 8BH,

serve per controllare e abilitare o disabilitare gli interrupt.

Nella sottostante tabella è riportato lo schema e la descrizione delle funzioni dei pin

di questo registro

Descrizione dei pin per la configurazione del registro INTCON1.

Bit

Symbol

Descrizione

7

GIE

Bit di abilitazione di tutti gli interrupt

6

EEIE

Bit di abilitazione dell’interrupt dopo la scrittura completa nella EEPROM

1 = abilita interrupt

0 = disabilita l’interrupt

5

T0IE

Bit di abilitazione dell’interrupt quando TMR0 va in overflow

1 = abilita l’interrupt

0 = disabilita l’interrupt

4

INTE

Bit di abilitazione dell’interrupt esterno RB0INT

1 = abilita l’interrupt

0 = disabilita l’interrupt

3

RBIE

Bit di abilitazione dell’interrupt quando un segnale del port RB cambia di stato

1 = abilita l’interrupt

0 = disabilita l’interrupt

2

T0IF

Bit di flag per rilevare l’overflow di TMR0

1 = TMR0 in overflow

0 = TMR0 non in overflow

1

INTF

Bit di flag dell’interrupt sul pin RB0/INT

1 = si è verificato un interrupt

0 = non si è verificato un interrupt

0

RBIF

Bit di flag che rileva l’interrupt causato da un cambiamento di un bit del Port RB

1 = si è verificato l’interrupt

0 = non si è verificato l’interrupt

Timer0 e Prescaler

Il modulo Timer0, che può fungere sia da timer sia da contatore, ha le seguenti proprietà:

• ha un formato da 8 bit;

• è scrivibile e leggibile;

• è possibile selezionare il clock interno e esterno;

• è possibile selezionare il fronte attivo del clock esterno;

• il prescaler a 8 bit è programmabile via software;

• l’interrupt per overflow da FFh a 00h

Per programmare il Timer0 come timer è necessario azzerare T0CS (OPTION_REG<5>).

È possibile leggere, tramite l’accumulatore W, il valore del Timer0 nel registro TMR0 prese-

-nte nel Bank 0 all’indirizzo 01H.

Il contenuto del TMR0 può anche essere programmato con un valore che il controllore

incrementerà a ogni ciclo di clock.

L’incremento o il decremento del TMR0 può essere causato da un clock interno o da un

clock esterno sul pin RA4/T0CKI.

Se in TMR0 si imposta un valore minore di 255, quando giunge alla fine del conteggio

(255), con il successivo impulso di clock (255+1), riparte con il conteggio da 0 e non

dal valore impostato.

Quando il TMR0 va in overflow, viene settato il bit T0IF del registro INTCONT.

Eventualmente si può far generare un segnale di interrupt settando il bit T0IE dello stesso

registro.

La modalità di funzionamento come contatore si ottiene settando il bit T0CS (OPTION_

REG<5>).

Nel modo contatore Timer0 sarà incrementato ogni volta che si avrà un fronte di salita o

discesa del segnale sul pin RA4/T0CKI.

Il fronte attivo del clock è ottenuto programmando il bit T0SE (OPTION_REG<4>).

Il micro dispone di un contatore programmabile a 8 bit che funge da divisore di frequenza

e svolge le seguenti funzioni:

• prescaler per il timer di sistema (Timer0);

• postscaler per il WatchDog.

Il circuito di prescaler è unico per il Timer0 e il WatchDog e quindi con il bit PSA (OPTION_

REG<3>) è selezionabile per l’uno o per l’altro.

Con i bit PS2-PS0 (OPTION_ REG<2:0>) si può selezionare il rapporto di prescaler.

Registri PORTA e TRISA

Il registro PORTA serve per leggere o scrivere un dato nella porta relativa.

Il PORTA è situato nel Bank 0 all’indirizzo 05h.

Il PORTA è un registro a 8 bit ma solo i primi

4 bit sono significativi.

Nella tabella a lato è riportata la descrizione

della funzione svolta dai pin.

Registro PORTA.

Bit

Symbol

Description

7

---

Non implementato, sempre a 0

6

---

Non implementato, sempre a 0

5

---

Non implementato, sempre a 0

4

RA4/T0CKI

Input di tipo TTL, uscita di tipo

open drain

Ingresso di clock esterno per

TMR0

3

RA3

I/O

2

RA2

I/O

1

RA1

I/O

0

RA0

I/O

Il registro TRISA, analogamente al PORTA,

è a 8 bit e solo i primi 4 sono significativi.

Si trova nel Bank 1 all’indirizzo 85H.

Questo registro serve per programmare quali

pin del PORTA devono essere di uscita e quali

di ingresso.

La scrittura nel TRISA non è diretta ma

avviene tramite il registro W (accumulatore).

Ponendo un bit del TRISA a 1 il corrispondente

pin del PORTA è programmato come bit

d’ingresso, se invece si mette a 0 il bit di

TRISA il bit corrispondente del PORTA è selezionato come bit di uscita.

Ad esempio se TRISA<1> = 1 allora PORTA<1> = ingresso.

Se TRISA<2> = 0 si ha PORTA<2> = uscita

Esempio

Programma di inizializzazione del PORTA.

BCF STATUS, RP0

;

CLRF PORTA

;Inizializza PORTA cancellando i dati in uscita

BSF STATUS, RP0

;seleziona Bank 1

MOVLW 0x0F

;valore usato per la direzione dati iniziale

MOVWF TRISA

;setta i bit RA<3:0> come ingressi ;RA4 come uscita TRISA<7:5>

;sono letti sempre come 0

Registri PORTB e TRISB

Il registro PORTB serve per leggere o scrivere un dato nella porta relativa.

Il PORTB è situato nel Bank 0 all’indirizzo 06h.

Il PORTB è un registro a 8 bit.

La descrizione delle funzioni svolte dai pin è riportata nella sottostante tabella:

Descrizione della funzione dei pin del PORTB

Bit

Symbol

Description

7

RB7

Ingresso TTL, uscita open drain

ingresso se TRISB7 = 1

ingresso interrupt, abilitato se RBIE = 1

weak pull-up programmabile internamente via software se RBPU = 0

6

RB6

Ingresso TTL, uscita open drain

ingresso se TRISB6 = 1

ingresso interrupt, abilitato se RBIE = 1

weak pull-up programmabile internamente via software se RBPU = 0

5

RB5

Ingresso TTL, uscita open drain

ingresso se TRISB5 = 1

ingresso interrupt, abilitato se RBIE = 1

weak pull-up programmabile internamente via software se RBPU = 0

4

RB4

Ingresso TTL, uscita open drain

ingresso se TRISB4 = 1

ingresso interrupt, abilitato se RBIE = 1

weak pull-up programmabile internamente via software se RBPU = 0

3

RB3

Ingresso TTL, uscita open drain

ingresso se TRISB3 = 1

weak pull-up programmabile internamente via software se RBPU = 0

2

RB2

Ingresso TTL, uscita open drain

ingresso se TRISB2 = 1

weak pull-up programmabile internamente via software se RBPU = 0

1

RB1

Ingresso TTL, uscita open drain

ingresso se TRISB1 = 1

weak pull-up programmabile internamente via software se RBPU = 0

0

RB0/INT

Ingresso TTL, uscita open drain

ingresso se TRISB0 = 1

ingresso interrupt se INTE = 1

weak pull-up programmabile internamente via software se RBPU = 0

Il registro TRISB, analogamente al PORTB, è a 8 bit.

Si trova nel Bank 1 all’indirizzo 86h.

Questo registro serve per programmare quali pin del PORTB devono essere di uscita e

quali di ingresso.

La scrittura nel TRISB è indiretta poiché passa attraverso l’accumulatore W.

Ponendo un bit del TRISB a 1 il corrispondente pin del PORTB è programmato come bit

d’ingresso, se invece si mette a 0 il bit di TRISB, il bit corrispondente del PORTB è

selezionato come bit di uscita.

Ad esempio se TRISB<1> = 1 allora PORTB<1> = ingresso.

Se TRISB<2> = 0 si ha PORTB<2> = uscita

Esempio

Programma di inizializzazione del PORTB.

BC STATUS, RP0

;

CLRF PORTB

;inizializza PORTB cancellando i dati in uscita

BSF STATUS, RP0

;seleziona Bank 1

MOVLW 0xCF

;valore usato per la direzione dati iniziale

MOVWF TRISB

;setta i bit RB<3:0> come ingressi

;RB<5:4> come uscite

;RB<7:6> come ingressi

Configurazione della CPU

Prima di iniziare l’elaborazione del programma utente è necessario configurare la CPU

inviando una configuration word da 14 bit.

La word di configurazione deve essere inviata alla CPU alla memoria codice all’indirizzo

2007h e deve essere ripetuta ogniqualvolta si esegue un aggiornamento del codice.

Nella sottostante tabella è riportato lo schema della configuration word.

Schema della configuration word.

Bit

Symbol

Description

13

CP = Code Protection

CP=1 codice non protetto

CP=0 Codice protetto

12

11

10

9

8

7

6

5

4

3

PWRTE

Power-up Timer Enable

PWRTE=1 Disabilitato

PWRTE=0 Abilitato

2

WDTE

WatchDog Timer Enable

WDTE=1 Abilitato

WDTE=0 Disabilitato

1

FOSC0

Oscillator Selection

0

FOSC1

Con CP = 0 il codice del programma è protetto da lettura; la EEPROM programma

risponde alla richiesta con 7Fh.

In questo caso si dice che il micro è OTP, programmabile una sola volta.

Si tratta di una modalità operativa utilizzata quando il codice non deve essere più

soggetto a modifiche.

La funzione svolta da bit PWRTE consiste nel tenere azzerata oppure no la CPU all’acce-

-nsione per un tempo di 72 ms in modo tale da consentire alla tensione di alimentazione

di raggiungere il valore standard.

Con PWRTE =1 la funzione è disabilitata, con PWRTE =0 la funzione è abilitata.

Il bit WDTE = 1 abilita la funzione di timer del watchdog; un livello 0 la disabilita.

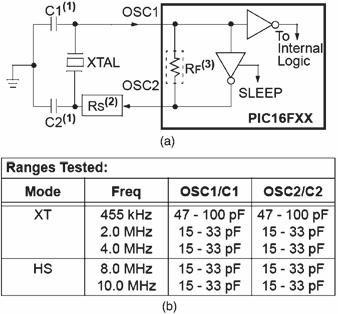

I bit F0SC0 e F0SC1 selezionano la tipologia circuitale dell’oscillatore:

• 00 = LP, oscillatore con cristallo a bassa potenza;

• 01 = XT, oscillatore al quarzo;

• 10 = HS, oscillatore al quarzo ad alta velocità;

• 11 = RC, oscillatore con componenti RC.

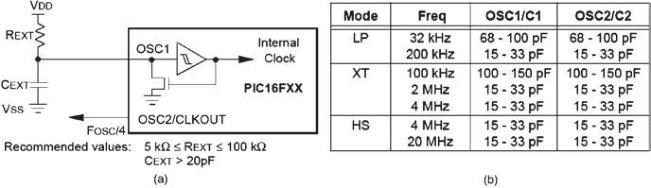

Nella figura (a) a lato è illustrato lo schema

circuitale che il costruttore suggerisce di adottare

per l’oscillatore al quarzo o con cristallo e in

figura (b) le relative frequenze con in valori

dei componenti.

Nella sottostante figura (a) è riportato invece lo

schema dell’oscillatore con componenti RC e

ella stessa figura (b) le relative frequenze con

i valori dei componenti

Set di istruzioni

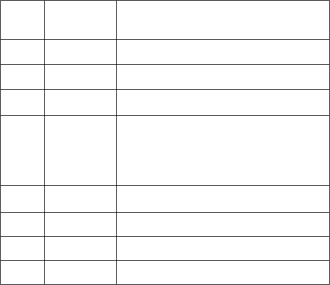

Le istruzioni del PIC16F84 sono classificabili in tre tipologie:

• istruzioni orientate al bit (tipo b);

• istruzioni orientate al byte (tipo B);

• istruzioni di controllo.

Ogni istruzione è eseguita in un ciclo macchina (4 cicli di clock) con l’eccezione delle

istruzioni di salto che necessitano di due cicli macchina.

Nelle sottostanti tabelle sono sintetizzate le istruzioni con una relativa breve descrizione.

Sintesi del set delle istruzioni.

Istruzione

Tipo

Status

Significato

Descrizione

Mnemonica

Parametro

ADDLW

K

(0<K<255)

B

C,DC,Z

Add Literal

and W

Somma la costante K al contenuto di W e pone

il risultato in W

ADDWF

f, d

B

C,DC,Z

Add W and f

Somma il contenuto di W e f:

se d = 1 risultato in f

se d = 0 risultato in W

ANDLW

K

(0<K<255)

B

Z

AND Literal

with W

Operazione AND tra contenuto di W e costante

K, risultato in W

ANDWF

f, d

B

Z

AND W with f

Operazione AND tra contenuto di W e di f:

se d = 1 risultato in f

se d = 0 risultato in W

BCF

f, b

b

Bit Clear f

Pone a 0 il bit b-esimo del registro f

BSF

f, b

b

Bit set f

Pone a 1 il bit b-esimo del registro f

BTFSC

f, b

c

Bit Test,

Skip if Clear

Test del bit b-esimo del registro f:

se b = 1 passa all’istruzione successiva

se b = 0 salta l’istruzione successiva con un

NOP

BTFSS

f, b

c

Bit Test,

Skip if Set

Test del bit b-esimo del registro f:

se b = 0 passa all’istruzione successiva

se b = 1 salta l’istruzione successiva con un

NOP

CALL

K

(0<K<2047)

c

Clear f

Resetta tutti i bit del registro f

CLRF

f

(0<f<2047)

B

Z

Clear f

Resetta tutti i bit del registro f

CLRW

B

Z

Clear W

Resetta 0 tutti i bit del’accumulatore W

CLRWDT

B

TO

PD

Clear

Watchdog

Timer

Resetta tutti i bit del WDT

COMF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

Z

Complement f

Complementa il registro f:

con d = 0 risultato in W

con d = 1 risultato in f

DECF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

Z

Decrement f

Decrementa il registro f:

con d = 0 risultato in W

con d = 1 risultato in f

DECFSZ

f,d

0 ≤ f ≤ 127

dε[0,1]

B/c

Decrement f,

Skip if 0

Decrementa il registro f:

con d = 0 risultato in W

con d = 1 risultato in f

ma se f = 0 salta l’istruzione

GOTO

K

0 ≤ K ≤

2047

c

Go To

Salto incondizionato alla locazione di

memoria programma K

INCF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

Z

Increment f

Incrementa il registro f:

con d = 0 risultato in W

con d = 1 risultato in f

INCFSZ

f,d

0 ≤ f ≤ 127

dε[0,1]

B/c

Z

Increment f,

Skip if 0

Incrementa il registro f:

con d = 0 risultato in W

con d = 1 risultato in f

ma se f = 0 salta l’istruzione

IORLW

K

0 ≤ f ≤ 255

B

Z

Inclusive OR

Literal with W

Operazione OR tra la costante k e il contenuto

di W, risultato in W

IORWF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

Z

Inclusive OR

E

with f

Operazione OR tra contenuto di W e contenuto

di f:

con d = 0 risultato in W

con d = 1 risultato in f

MOVF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

Z

Move f

Con d = 0 contenuto di f in W

Con d = 1 contenuto di f in f (debug)

MOVLW

K

0 ≤ f ≤ 255

B

Move Literal

to W

Pone in W la costante K

MOVWF

f,d

0 ≤ f ≤ 127

B

Move W to f

Trasferisce il contenuto di W in f

NOP

No Operation

Nessuna operazione

RETFIE

c

Return from

Interrupt

Servita la subroutine di servizio dell’interrupt

torna al punto in cui aveva interrotto il main

RETLW

K

c

Return with

Literal W

Servita la subroutine di servizio dell’interrupt

torna al punto in cui aveva interrotto il main

Pone in W la costante K

RETURN

c

Return from

subroutine

Servita la subroutine torna al punto in cui

aveva interrotto il main

RLF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

C

Rotate Left

through Carry

Shifta a sinistra i bit del registro f. Il bit nel

flag C dello STATUS viene posto nella posizione

0 del risultato, il bit 7 viene posto in C:

Con d = 0 risultato in W

Con d = 1 risultato in f

RRF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

C

Rotate Right

through Carry

Shifta a destra i bit del registro f. Il bit C dello

STATUS viene posto nella posizione 0 del

risultato, il bit 7 viene posto in C:

Con d = 0 risultato in W

Con d = 1 risultato in f

SLEEP

c

TO

PD

Sleep

CPU in standby

Da questo stato la CPU esce con un interrupt

Ma non da timer interno o con un reset

dall’esterno

SUBLW

K

B

C,DC,Z

Subtract

Literal

from W

Sottrae dal contenuto di W la costante K e il

risultato in W.

SUBWF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

C,DC,Z

Subtract W

from f

Sottrae dal contenuto di W il contenuto di f:

con d = 0 risultato in W

con d = 1 risultato in f

SWAPF

f,d

0 ≤ f ≤ 127

dε[0,1]

B

Swap Nibbles

in f

Scambia la parte alta con quella bassa del

registro f:

con d = 0 risultato in W

con d = 1 risultato in f

XORLW

K

0 ≤ f ≤ 255

B

Z

Exclusive OR

Literal with W

Operazione XOR tra K e contenuto di W,

risultato in W

XORWF

f,d

0 ≤ f ≤ 127

dε[0,1

B

Z

Exclusive OR

Literal with f

Operazione XOR tra contenuto di W e di f:

con d = 0 risultato in W

con d = 1 risultato in f

Istruzioni booleane

Mnemonic

Operation

Execution Time

(ms)

ANL C, bit

C=C and bit

2

ANL C, /bit

C=C and not bit

2

OR C,bit

C= C or bit

2

OR C, /bit

C= C or not bit

2

MOV C, bit

C=bit

1

MOV bit, C

Bit=C

2

CLR C

C=0

1

CLR bit

Bit=0

1

SETB C

C=1

1

SETB bit

Bit=1

1

CPL C

C=not C

1

CPL bit

Bit=not bit

1

JC rel

Se C=1 salta

2

JNC rel

Se C=0 salta

2

JB bit, rel

Se bit=1 salta

2

JNB bit, rel

Se bit=0 salta

2

JBC bit, rel

Se bit=0 salta e poni bit=0

2

Linguaggi di programmazione

Il linguaggio di programmazione dei microcontrollori, come quelli dei microprocessori, è

un linguaggio Assembler.

Prima di essere installato in un micro il programma in Assembler deve essere compilato.

La compilazione consiste nel tradurre il programma scritto in linguaggio Assembler, ovvero

in un codice mnemonico, in un linguaggio macchina, una sequenza di bit 0 e 1.

I programmi in linguaggio Assembler hanno estensione «.asm».

Tuttavia anche la programmazione in Assembler è meno agevole rispetto alla program-

-mazione con linguaggi ad alto livello poiché il linguaggio di basso livello è strettamente

legato al tipo di micro o comunque alla famiglia di micro.

Risulta pertanto più agevole la programmazione con linguaggio ad alto livello che, essendo

svincolata dal micro, è esportabile su altri dispositivi.

In questo caso sono necessari compilatori in grado di tradurre il programma scritto con

linguaggi ad alto livello in linguaggio macchina.

I linguaggi ad alto livello più diffusi sono Basic, C e Pascal.

Sono disponibili oggi oltre ai compilatori professionali anche quelli di tipo open source.

Per rendere più agevole il compito del progettista, la MICROCHIP, produttrice dei micro PIC,

distribuisce gratuitamente un sistema di sviluppo integrato IDE (Integrated Development

Environment) chiamato MPLAB.

Un sistema integrato di sviluppo consente la scrittura, il debug e la simulazione del

programma da installare nel micro. MPLAB è una suite per Windows che comprende un

ambiente di sviluppo grafico, assembler e debugger.

MPLAB non è però un compilatore.

Il compilatore a volte è fornito anche gratuitamente dall’azienda che produce il program-

-matore.

Il programmatore è un circuito che serve per eseguire il trasferimento del file eseguibile

nel PIC.

Il programmatore e il relativo software costituisce l’interfaccia tra il PC e la scheda su

cui è residente il PIC.

La porta di comunicazione del PC è normalmente la seriale RS232.

La sottostante tabella evidenzia le differenti prestazioni del PIC16F84A rispetto a quelle dei

modelli superiori 16F628 e 16F819.

Caratteristiche differenti dei modelli 16F84A, 16F628 e 16F819

Caratteristiche

PIC 16F84A

PIC 16F628

PIC 16F819

Linee I/O

13

16

16

Mem. FLASH (programma)

1 Kilobyte

2 Kilobyte

2 Kilobyte

Mem. RAM (dati volat.)

68 byte

224 byte

256 byte

Mem. EEPROM (dati non volat.)

64 byte

128 byte

256 byte

Timer

1 (a 8 bit)

2 (a 8 bit)

1 (a 16 bit)

2 (a 8 bit)

1 (a 16 bit)

Comparatori analogici

No

2

1

Funzione Capture

(misura intervalli di tempo)

No

Si

Si

Funzione Compare

(confronto conteggio)

No

Si

Si

Uscita PWM

No

Si (risoluz. 10bit)

Si (risoluz. 10bit)

Convertitore A/D

No

No

5 canali da 10bit

Porta Seriale

No

Si

Si

Lorem Ipsum Dolor

Cupidatat excepteur ea dolore sed in adipisicing id? Nulla lorem deserunt aliquip officia reprehenderit fugiat, dolor excepteur in et officia ex sunt ut, nulla consequat. Laboris, lorem excepteur qui labore magna enim ipsum adipisicing ut. Sint in veniam minim dolore consectetur enim deserunt mollit deserunt ullamco. Mollit aliqua enim pariatur excepteur. Labore nulla sunt, in, excepteur reprehenderit lorem fugiat. Ipsum velit sunt! Non veniam ullamco amet officia ut, ex mollit excepteur exercitation fugiat eu ut esse cupidatat in velit. Non eu ullamco in pariatur nisi voluptate mollit quis sed voluptate ea amet proident dolore elit. Occaecat nostrud dolore sunt, ullamco eu ad minim excepteur minim fugiat. Nostrud culpa eiusmod dolor tempor et qui mollit deserunt irure ex tempor ut dolore. Dolore, nostrud duis ad. In nulla dolore incididunt, sit, labore culpa officia consectetur mollit cupidatat exercitation eu. Aute incididunt ullamco nisi ut lorem mollit dolore, enim reprehenderit est laborum ut et elit culpa nulla. Excepteur fugiat, laboris est dolore elit. In velit lorem id, et, voluptate incididunt ut ad in sunt fugiat, esse lorem. Nisi dolore ea officia amet cillum officia incididunt magna nisi minim do fugiat ut nostrud dolore Qui in est in adipisicing ea fugiat aliqua. Reprehenderit excepteur laboris pariatur officia sit amet culpa aliquip quis elit eiusmod minim. Sint ut ut, proident in mollit do qui eu. Pariatur et cupidatat esse in incididunt magna amet sint sit ad, sunt cillum nulla sit, officia qui. Tempor, velit est cillum sit elit sed sint, sunt veniam.

© Irure ut pariatur ad ea in ut in et. In incididunt sed tempor