È un'abitudine ridicola degli esseri umani il correre più veloci quando hanno perso la strada.

MICROPROCESSORI E MICROCONTROLLORI

… studiare, studiare ed ancora studiare,

è il solo modo di capire quanto possa

essere grande sia la propria ignoranza!

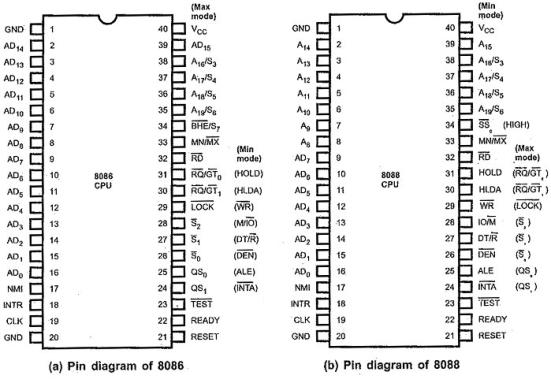

ANCORA SUL MICROPROCESSORE 8086-8088

Descrizione della piedinatura e dei segnali

I segnali d’ingresso e di uscita dai piedini del microprocessore

sono disegnati nelle sottostanti figure (a) e (b).

Indipendentemente dal tipo di funzionamento (minimo o massimo) i segnali relativi ai 40 pin

dell’integrato possono essere classificati in:

• segnali di alimentazione (VCC e GND);

• segnale di clock;

• indirizzi e dati;

• segnali di controllo e di stato.

I segnali di alimentazione, clock e indirizzi/dati, sono comuni ai due tipi di funzionamento,

quelli di controllo e di stato saranno invece classificati in comuni e specializzati.

I segnali di alimentazione e clock

I pin dell’alimentazione sono tre: due per la

massa (1 e 20) ed uno per VCC (40).

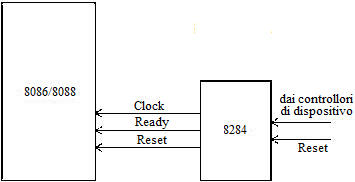

Il segnale di clock (19) va in ingresso

al microprocessore e proviene direttamente

dall’integrato generatore di clock 8284

(evidenziato a lato).

I segnali indirizzi e dati

I segnali relativi agli indirizzi e ai dati sono indipendenti dal tipo di funzionamento.

Nell’8086 i 16 bit meno significativi del bus indirizzi sono condivisi con il bus

dati mentre i 4 bit di peso superiore sono in comune con alcuni segnali di stato .

Nell’8088 invece le linee del bus dati sono multiplexate solo sugli 8 bit meno significativi.

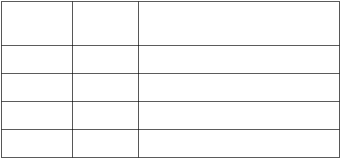

I segnali di controllo e di stato

Le linee di stato sono di uscita dal processore ma solo in alcuni istanti perché sono

multiplexati con altri segnali. servono a informare sull’attività svolta

dal microprocessore; sono disponibili solo nel funzionamento in modo massimo.

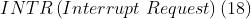

I bit hanno un significato

complessivo: servono a identificare il registro di

segmento utilizzato per generare l’indirizzo

durante il ciclo di bus, come evidenziato nella

tabella a lato .

è sempre uguale a 0 mentre riflette

il bit di interrupt del registro dei flags, per

l’8086 è un bit di stato di ricambio.

I segnali di controllo regolano il rapporto del

microprocessore con tutti gli altri componenti del sistema:

• provvedono a porre sull’address bus l’indirizzo;

• a informare se un dato deve essere letto o scritto nella memoria o in un dispositivo di I/O;

• ad abilitare la memoria o l’I/O ecc.

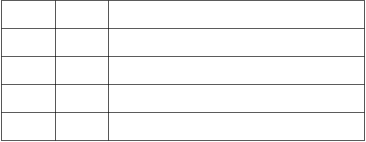

Selezione del registro segmento.

S3

S4

Registro di segmento

0

0

ES (extra)

1

0

SS (stack)

0

1

CS/ -codice nessuno

1

1

DS (dati)

I segnali di controllo comuni ai due tipi di funzionamento sono: .

L’uscita , presente solo nell’8086, serve a interfacciare il microprocessore con

dispositivi aventi un data bus a 8 bit.

Se l’indirizzo generato dalla CPU è pari si possono verificare due casi:

•

, il dato da caricare è una parola (16 bit);

•

, deve essere caricato solo il byte alto.

Se l’indirizzo è invece dispari , il microprocessore carica il dato, sempre un byte

alla volta (anche se è a 16 bit), tenendo quindi .

Il segnale può essere interpretato come settimo bit di stato (S7) che informa

sulla lunghezza del dato.

è un segnale di uscita che indica quando la CPU esegue un’operazione di lettura

(dalla memoria o da un I/O).

La linea è un ingresso per il microprocessore e proviene dal generatore di clock

8284 (vedi la soprastante figura).

Questa linea viene attivata da dispositivi (periferica o memoria) caratterizzati da un

comportamento temporale più lento per far inserire stati di attesa (wait states) nei cicli di

bus allo scopo di sincronizzare il funzionamento del microprocessore.

Il arriva all’8086/8088 tramite l’integrato 8284; la linea che deve restare attiva

per almeno 4 colpi di clock è impiegata per inizializzare il processore.

Produce lo stesso effetto dello spegnimento e della riaccensione dell’alimentazione: la coda

delle istruzioni viene cancellata, sono resettati i registri di stato, l’IP, i registri segmento, lo

stack e l’extra mentre il registro segmento del codice viene settato a .

Il microprocessore riparte leggendo il primo byte dalla locazione di memoria .

L’ , è un segnale del sistema di interruzione dell’8086/8088.

È un ingresso attivo a livello alto e proviene direttamente dagli I/O o da un controllore

delle interruzioni (PIC 8259).

L’interrupt generale prodotto da un dispositivo serve a segnalare la necessità di essere

serviti.

Tale richiesta può essere ignorata (cioè mascherata) con un apposito comando software

inviato alla CPU.

L’8086/8088, alla fine di ogni ciclo di fetch, controlla lo stato di questa linea e se la trova

attiva, esegue il programma di servizio dell’interruzione.

L’ingresso è un segnale di interrupt che la CPU

non può ignorare (interruzione non mascherabile). Quando la linea NMI viene attivata

da un organo periferico, il microprocessore sospende l’esecuzione del programma in corso ed

esegue la relativa routine di servizio.

L’ingresso sovrintende al funzionamento della CPU quando è collegata ad un

coprocessore come per esempio il processore matematico 8087. Se la linea è attiva,

il microprocessore sospende qualsiasi attività e si pone in idle state permettendo al copro-

-cessore lo svolgimento delle sue operazioni.

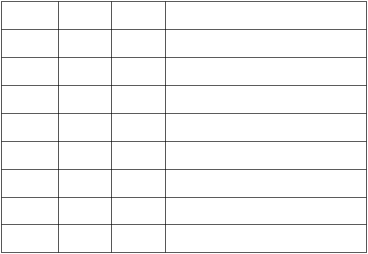

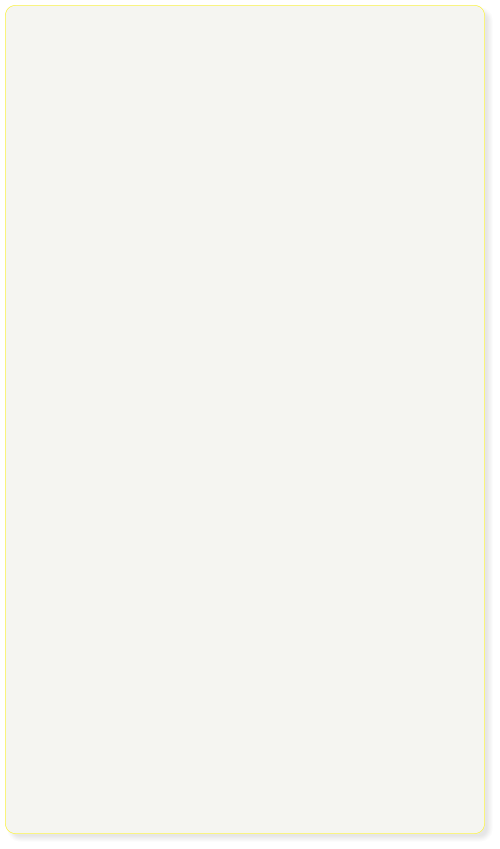

Tabella di identificazione del ciclo di bus

Ciclo di bus

0

0

0

Riconoscimento interruzione

0

0

1

Lettura I/O

0

1

0

Scrittura I/O

0

1

1

Alt

1

0

0

Prelievo Istruzione

1

0

1

Lettura dalla Memoria

1

1

0

Scrittura in Memoria

1

1

1

Nessun Ciclo di Bus

Segnali relativi al modo minimo

L’uscita , che funziona come uno strobe, è attivata dal microprocessore

quando deve eseguire una operazione di scrittura in memoria o in un dispositivo di I/O.

Attivando la linea , il microprocessore abilita la memoria o gli

I/O a mettere il dato sul bus mentre con l’uscita la CPU segnala di aver posto

sull’address bus un indirizzo valido.

L’uscita , sta a indicare il dispositivo con cui deve

dialogare la CPU.

Nell’8088 la linea ha i livelli attivi opposti: .

Se si associa alla linea , è possibile stabilire la

direzione del flusso dei dati: con i dati vengono ricevuti mentre con

sono trasmessi dalla CPU verso l’esterno.

L’8088 è dotato di un’uscita che sostituisce .

unitamente alle linee e fornisce una decodifica dello stato del ciclo di bus.

L’uscita , quando attivata indica al dispositivo richiedente

il riconoscimento dell’interruzione pervenuta tramite la linea

.

L’ingresso e l’uscita fanno parte del sistema di controllo della

proprietà del bus.

Se un altro processore oppure il controllore DMA chiede il controllo del bus, attiva la linea

(livello 1); in risposta l’8086/8088 pone in tristate le linee di indirizzo/dati e quasi

tutti i segnali di controllo, contemporaneamente attiva per segnalare al dispositivo

richiedente la possibilità di assumere il comando del bus.

Terminate le operazioni il processore alternativo o il DMA invia un ulteriore segnale sulla

linea e l’8086/8088 riprende tutte le funzioni di controllo.

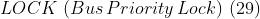

Segnali relativi al modo massimo

Nel funzionamento in modo massimo l’8086/8088 necessita di due chip di interfaccia: uno

per il controllo del bus (8288), un altro per la gestione delle priorità del bus (8289).

In tal modo molti pin del microprocessore vengono liberati dalla loro funzione e sono

utilizzati per gestire il sistema in multiprocessing.

In modo massimo il microprocessore non genera direttamente i segnali per gestire la

memoria e gli I/O ma fornisce i segnali , lo stato dei quali identifica il ciclo di bus

da eseguire, come nella tabella a lato.

Tali segnali costituiscono gli ingressi per

l’arbitro (8259) e il controllore (8288) del bus.

In particolare quest’ultimo provvede a sua

volta a generare tutti i segnali necessari per

la lettura e la scrittura in memoria, la lettura

e la scrittura in un I/O, il riconoscimento di

una richiesta di interruzione.

L’uscita ,

ingresso dell’arbitro del bus (8289), serve per

comunicare agli altri processori che non è

possibile acquisire il controllo del sistema.

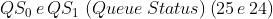

sono i

segnali di stato per la coda di istruzioni

(verdi tabella a destra). I due segnali.

,

richiesta/assegnazione, operano nello

stesso modo di

per

trasferire il controllo del bus.

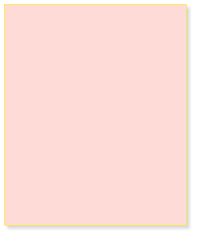

Tabella di identificazione della coda delle istruzioni

Stato della Coda

0

0

Nessuna operazione

0

1

Prelevamento primo byte istruzione

1

0

Reinizializzazione/salto

1

1

Prelevamento secondo byte istruzione

Modi di indirizzamento

I modi di indirizzamento possono essere:

• implicito;

• immediato;

• con registro;

• diretto;

• indiretto a registro;

• indiretto a registro con spostamento;

• indiretto a registro base e indice;

• indiretto a registro base + indice + costante.

Indirizzamento implicito

Nel modo di indirizzamento implicito l’operando non appare perché è implicito all’istruzione

stessa.

Ad esempio STI significa metti a 1 il flag delle interruzioni.

L’operando quindi non è specificato poiché è già noto al microprocessore.

Indirizzamento immediato

Nel metodo di indirizzamento immediato l’operando, in genere una costante, è indicato

nell’istruzione stessa:

MOV AX,0B1.

Il significato dell’istruzione è il seguente: mettere nel registro AX il valore esadecimale B1H.

Indirizzamento con registro

In questo tipo di indirizzamento il microprocessore utilizza i registri interni (AX, BX, CX e

DX) e non deve generare un indirizzo per reperire l’operando.

Un esempio è l’istruzione MOV AX,BX.

Il contenuto del registro BX viene copiato nel registro AX.

Analogamente l’istruzione MOV AL,BL serve a copiare il contenuto di BL in AL.

L’esecuzione di queste istruzioni non richiede la generazione di un indirizzo poiché l’opera-

-zione è svolta tutta internamente al microprocessore.

Indirizzamento diretto

Con l’indirizzamento diretto viene specificato direttamente l’indirizzo della locazione

di memoria in cui è contenuto l’operando;

ad esempio MOV AX,COST.

Il valore della COST (costante) viene utilizzato come offset per la generazione dell’indirizzo

a 20 bit.

Infatti COST è combinato nel BIU con il contenuto del registro segmento DS assunto come

registro di default.

È possibile specificare il registro segmento desiderato con l’istruzione:

MOV AX,CS:COST.

L’indirizzo è ottenuto usando il contenuto del registro CS come prefisso di override e la

costante come offset.

Indirizzamento indiretto a registro

Un esempio di indirizzamento indiretto a registro è

MOV AX,[BX].

Il suo significato è il seguente: copia in AX l’operando il cui indirizzo è contenuto nel regi-

-stro segmento DS e il cui offset è dato dal registro BX.

L’offset può essere contenuto in generale in un registro di base o in un registro indice:

BX, BP, SI e DI.

Indirizzamento indiretto a registro con spostamento

Questo tipo di indirizzamento rappresenta una sintesi dei due indirizzamenti precedenti;

ad esempio MOV AL, COST [DI].

L’indirizzo dell’operando da inserire in AL è indicato indirettamente:

l’offset, da combinare con il contenuto del registro DS, è ottenuto sommando il valore della

COST e del contenuto del registro DI.

Indirizzamento indiretto a registro base e indice

In questo tipo di indirizzamento l’offset dell’indirizzo dell’operando viene ottenuto som-

-mando il contenuto di due registri interni.

Esempio di istruzione: MOV AH,[BX] [DI].

Indirizzamento indiretto a registro base indice + costante

L’offset dell’indirizzo dell’operando si ottiene sommando il contenuto del registro base, il

contenuto del registro indice e il valore della costante; ad esempio

MOV AH, COST [BX] [SI].

Lorem Ipsum Dolor

Cupidatat excepteur ea dolore sed in adipisicing id? Nulla lorem deserunt aliquip officia reprehenderit fugiat, dolor excepteur in et officia ex sunt ut, nulla consequat. Laboris, lorem excepteur qui labore magna enim ipsum adipisicing ut. Sint in veniam minim dolore consectetur enim deserunt mollit deserunt ullamco. Mollit aliqua enim pariatur excepteur. Labore nulla sunt, in, excepteur reprehenderit lorem fugiat. Ipsum velit sunt! Non veniam ullamco amet officia ut, ex mollit excepteur exercitation fugiat eu ut esse cupidatat in velit. Non eu ullamco in pariatur nisi voluptate mollit quis sed voluptate ea amet proident dolore elit. Occaecat nostrud dolore sunt, ullamco eu ad minim excepteur minim fugiat. Nostrud culpa eiusmod dolor tempor et qui mollit deserunt irure ex tempor ut dolore. Dolore, nostrud duis ad. In nulla dolore incididunt, sit, labore culpa officia consectetur mollit cupidatat exercitation eu. Aute incididunt ullamco nisi ut lorem mollit dolore, enim reprehenderit est laborum ut et elit culpa nulla. Excepteur fugiat, laboris est dolore elit. In velit lorem id, et, voluptate incididunt ut ad in sunt fugiat, esse lorem. Nisi dolore ea officia amet cillum officia incididunt magna nisi minim do fugiat ut nostrud dolore Qui in est in adipisicing ea fugiat aliqua. Reprehenderit excepteur laboris pariatur officia sit amet culpa aliquip quis elit eiusmod minim. Sint ut ut, proident in mollit do qui eu. Pariatur et cupidatat esse in incididunt magna amet sint sit ad, sunt cillum nulla sit, officia qui. Tempor, velit est cillum sit elit sed sint, sunt veniam.

© Irure ut pariatur ad ea in ut in et. In incididunt sed tempor