Non sei mai troppo piccolo per fare la differenza

ELETTRONICA DIGITALE

… studiare, studiare ed ancora studiare,

è il solo modo di capire quanto possa

essere grande sia la propria ignoranza!

LE MEMORIE

La memoria si può considerare come un archivio o un magazzino

contenente le informazioni, scritte in un qualsiasi codice binario e

consultabili in qualsiasi istante su richiesta.

Nei sistemi a logica cablata possono essere considerate vere e

proprie memorie i convertitori di codice, i generatori di caratteri

(ad esempio i decoder/driver per display a matrice di punti),

i registri di memoria e i registri a scorrimento.

La memoria viene usata quindi dal microprocessore come area

di lavoro, oltre che come archivio di dati e pertanto, tanto più

grande è, tanto più complesso è il programma che può essere

eseguito.

Le memorie a semiconduttore hanno minore capacità rispetto a quelle di massa ma hanno

un tempo di accesso più basso (velocità operativa più elevata) e un costo più elevato, anche

se le moderne tecnologie LSI e VLSI, consentendo un grande aumento del numero di bit

sullo stesso chip, hanno portato a una diminuzione considerevole del prezzo.

Caratteristiche e classificazione

Una memoria è costituita da un insieme di locazioni o di celle in grado di contenere un dato,

formato da un bit o un gruppo di bit.

Ogni locazione di memoria è individuata da un unico indirizzo.

L’indirizzo è una parola espressa in binario; quando la memoria è molto grande, poiché

l’indirizzo è molto esteso, è conveniente fare uso della codifica esadecimale.

Ad esempio, se una memoria può contenere 64 K parole, i suoi indirizzi vanno da

0000 0000 0000 0000 a 1111 1111 1111 1111.

Sono necessari 16 bit per ogni indirizzo dato che 64 K = 64 · 1024 = 65 536 =

.

Usando la numerazione esadecimale risulta più facile la lettura degli indirizzi: da (0000)16

a (FFFF)16.

Nella figura a lato è riportato un esempio di memoria costituita

da 8 locazioni, contenenti ciascuna dati di 4 bit, con una capacità

totale di 32 bit.

Non esiste nessuna relazione che lega il numero dei bit degli

indirizzi al numero dei bit dei dati.

Per accedere a ogni locazione di memoria è necessario cono-

-scere il relativo indirizzo.

Al fine di una valutazione delle prestazioni di una memoria

si definiscono i seguenti parametri:

Esempio di organizzazione di una

memoria con capacità di 32 bit.

•

capacità o densità = numero massimo di bit memorizzabili; l’unità di misura è il

kilobit: 1 Kb = 1 ·

bit =1024 bit; ad esempio 8 Kb corrispondono a

8 · 1024 bit = 8192 bit;

•

organizzazione interna = struttura interna che determina le modalità di accesso alle

singole locazioni;

•

consumo di potenza = assorbimento di potenza dall’alimentatore in condizioni di

lavoro e di standby;

•

tensioni limiti di funzionamento = valori delle tensioni di esercizio della memoria e

relative tolleranze;

•

tempo di accesso = intervallo di tempo che intercorre tra l’istante in cui viene posto in

ingresso l’indirizzo e l’istante in cui il dato relativo è effettivamente disponibile in uscita;

è un indice della velocità operativa dell’integrato;

•

tempo di ciclo = tempo necessario per effettuare l’intera operazione di lettura o di scrit-

-tura o lettura/scrittura;

•

data remanence = è il residuo dei dati contenuti nella memoria anche dopo un’opera-

-zione di cancellazione;

•

larghezza di banda = numero di bit in grado di essere trasferiti (in ingresso o in uscita)

nell’unità di tempo;

•

latenza = tempo di ritardo nell’eseguire l’operazione;

•

ritenzione = capacità di mantenere il dato nel tempo;

•

endurance = numero di cicli di lettura/scrittura che possono essere eseguiti con la

garanzia del corretto funzionamento dell’integrato; naturalmente questo parametro è

riferito alle memorie che possono essere cancellate e riprogrammate

Valutando le modalità operative, si possono distinguere le memorie secondo le seguenti

caratteristiche:

•

volatilità = perdita definitiva dei dati memorizzati quando viene a mancare la tensione

di alimentazione oppure quando questa scende al di sotto di un valore limite;

•

non volatilità = capacità di mantenere i dati anche in assenza della tensione di

alimentazione;

•

ad accesso casuale (random access memory) = modalità di accesso a una qualsiasi

locazione con un tempo medio costante che non dipende dalla posizione spaziale

occupata nell’interno della memoria; queste memorie sono anche conosciute come

memorie ad accesso spaziale;

•

ad accesso sequenziale = modalità di accesso a una locazione con un tempo dipendente

dalla posizione della locazione; sono conosciute anche come memorie ad accesso

temporale; il dato viene raggiunto scorrendo in sequenza tutti gli indirizzi fino a trovare

la locazione desiderata;

•

a sola lettura = capacità di memorizzare i dati ma non di cambiarli; le memorie di

questo tipo sono definite ROM (Read Only Memory)

•

a lettura/scrittura = capacità di memorizzare e cambiare i dati contenuti; le memorie

sono definite RWM (Read Write Memory);

•

statica = tecnica circuitale che consente di memorizzare l’informazione indefinitamente

fintantoché l’integrato è alimentato; ogni cella di memoria è costituita in genere da un

flip-flop;

•

dinamica = tecnica circuitale che consente di memorizzare il dato in un condensatore;

poiché questo tende a scaricarsi deve essere rinfrescato dopo un periodo di 2 ms circa.

Le memorie a semiconduttore sono fondamentalmente di due tipi: ROM e RAM.

Le ROM (Read Only Memory) sono memorie a sola lettura, contengono informazioni a

carattere permanente e possono essere solo statiche.

Le RAM (Read Access Memory) sono memorie a lettura e scrittura, sono destinate a

contenere dati modificabili in fase di elaborazione.

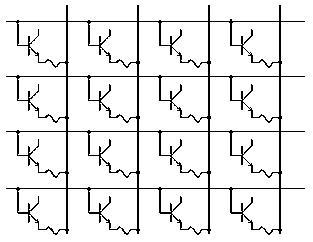

L’architettura interna delle ROM e delle RAM è costituita essenzialmente da locazioni di

memoria (tipo registri) disposte seconda una matrice di righe e colonne.

La posizione di una locazione è individuata da una particolare riga e da una certa colonna.

Il numero r di righe individua il numero di dati che la memoria contiene, mentre il

numero c delle colonne coincide con i bit del dato.

Una matrice di r righe e c colonne avente dimensione r × c, con r =

e n = numero di bit

di indirizzo, risulta però fortemente sbilanciata.

Per ovviare a questo inconveniente sulla stessa riga vengono allocati più dati in modo tale

da formare una matrice con un aspetto quasi quadrato.

Quando viene abilitata una riga è poi necessario l’uso di un multiplexer per selezionare,

tra tutte le locazioni presenti su quella riga, quelle da leggere o scrivere.

Entrambe le memorie possono essere costruite sia in tecnologia bipolare che unipolare.

In figura [A] è indicata una prima classificazione secondo la tecnologia di costruzione.

Una ulteriore classificazione è possibile seguendo il criterio delle modalità operative,

come indicato in figura [B].

Classificazione delle memorie secondo la

tecnologia di costruzione

[B]

[A]

Classificazione delle memorie

secondo le modalità operative

Memorie a lettura e scrittura (RAM)

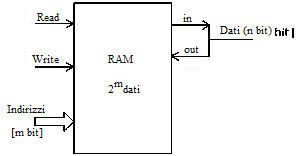

La RAM è una memoria a lettura e scrittura, ad accesso casuale e volatile.

Poiché esistono altri tipi di memorie ad accesso casuale, sarebbe più

esatta la denominazione di RWM, come fanno alcuni costruttori.

La RAM è utilizzata anche come memoria cache perché è sufficientemente

veloce per poter dialogare con una CPU e ha un consumo di potenza

abbastanza contenuto. In figura a lato è rappresentato

il simbolo di una RAM contenente

parole ognuna

a n bit.

L’operazione di scrittura consiste nell’introdurre nella

memoria dei dati diversi da quelli precedenti, che

vengono quindi definitivamente persi.

Tale operazione può essere ripetuta illimitatamente.

Le fasi dell’operazione di scrittura sono descritte dai

diagrammi del ciclo di scrittura forniti dalla casa

costruttrice.

L’operazione di lettura consente di leggere nella

locazione desiderata senza alterarne il contenuto.

Anche in questa operazione vengono forniti dal costruttore i diagrammi dei tempi del ciclo.

Con riferimento alle linee d’ingresso e di uscita che compaiono nel soprastante simbolo

logico , definiamo i criteri generali per le modalità operative delle RAM.

Simbolo logico di una RAM con

2m dati da n bit

•

Operazione di lettura:

– si seleziona la locazione a cui si desidera accedere ponendo l’indirizzo sulle linee

Indirizzi;

– si attiva la linea Read;

- Il dato contenuto nella locazione indirizzata viene posto sulla linea bidirezionale

Dati, che in questo caso funge da uscita (out); è necessario sottolineare che esiste

un ritardo di tempo tra l’istante in cui il segnale Read è abilitato e l’istante in cui il

dato richiesto è effettivamente disponibile in uscita; è dunque indispensabile

conoscere i tempi di ciclo di una memoria.

•

Operazione di scrittura:

– si seleziona la locazione a cui si desidera accedere ponendo l’indirizzo sulle linee

Indirizzi;

– si attiva la linea Write;

– si pone sulla linea bidirezionale Dati, che in questo caso funge da ingresso (in), la

parola da memorizzare; tale dato deve essere mantenuto in ingresso per un certo

intervallo di tempo; la parola precedentemente memorizzata viene così sostituita.

Le tecniche di accesso alle varie locazioni, sia in caso di scrittura che di lettura, possono

essere diverse e comunque dipendono dall’organizzazione interna del dispositivo.

Le RAM, statiche e dinamiche, sono dotate internamente di un circuito di precarica

(precharge) che serve a evitare il degrado delle prestazioni della memoria causate

dal fenomeno della latenza.

Dopo un’operazione di lettura o scrittura le linee devono essere riportate a riposo per

predisporre la memoria all’operazione successiva.

L’intervallo di tempo tra un’operazione e la successiva prende il nome di intervallo di

precarica.

Allo scopo di ridurre tale intervallo, un comando esterno, tenendo conto del tempo neces-

-sario per il completamento di un’operazione di lettura/scrittura, attiva il circuito di

precarica, velocizzando in questo modo la disponibilità della RAM.

RAM statica

La RAM statica (SRAM) è costituita essenzialmente da una matrice di flip-flop; se viene a

mancare la tensione di alimentazione il dato è irrimediabilmente perduto.

In una RAM statica, a differenza di un RAM dinamica, l’operazione di lettura non è

distruttiva, ovvero i dati contenuti nelle memoria non vengono alterati.

La SRAM è caratterizzata soprattutto da una buona velocità di funzionamento e da

un basso consumo.

Il consumo di potenza delle SRAM è estremamente basso (μW) quando la memoria è in

standby, mentre durante gli accessi dipende dalla frequenza di funzionamento.

Tale consumo aumenta all’aumentare della frequenza specialmente quando si porta la

velocità a pieno regime.

Se i microprocessori con cui lavorano le SRAM non sono particolarmente veloci, il consumo

è abbastanza contenuto.

Le RAM statiche sono caratterizzate da un circuito interno più complesso rispetto alle RAM

dinamiche, per cui sono meno dense e hanno una capacità di bit più bassa.

Dunque, a parità di spazio, il numero di bit in una SRAM è minore e quindi il costo per bit

è superiore.

La buona velocità di funzionamento, pagata con una occupazione di spazio molto alta, è

dovuto al fatto che l’accesso in lettura/scrittura ha un protocollo semplice e veloce:

l’indirizzo viene mandato in una sola soluzione insieme ai segnali di controllo.

I dati vengono letti o scritti sul bus accessibile

all’esterno.

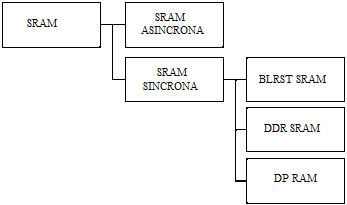

Nella figura a lato è riportata una possibile

classificazione delle RAM statiche tenendo

presente però che è difficile avere una visione

completa dei prodotti, sia perché in commercio

ne esiste una grande varietà sia per la velocità

tumultuosa del progresso tecnologico.

Classificazione delle RAM statiche

•

La SRAM asincrona è così chiamata perché la sua interfaccia con il bus

di sistema è completamente asincrona, pertanto ha un funzionamento

indipendente dal clock della CPU.

Ne consegue che durante le operazioni di lettura o scrittura, la CPU può essere costretta

a introdurre nei cicli operativi degli stati di attesa (wait state) se la memoria non è

pronta al dialogo.

La SRAM asincrona è utilizzata come cache di secondo livello e raramente come

memoria principale di un sistema a microprocessore.

•

La SRAM sincrona invece è dotata di un’interfaccia sincrona con il bus di sistema, quindi

ha un funzionamento che è in sincronismo con il clock della CPU.

I tempi di accesso ai dati memorizzati nel chip sono più brevi.

•

Le Burst SRAM, conosciute anche come SyncBurst SRAM, hanno un funzionamento

sincrono con il clock di sistema e una struttura pipeline, perché sono specializzate nel

trasferimento di pacchetti di dati.

Sono utilizzate soprattutto come cache memory esterne di primo e secondo livello in

tutti i sistemi in cui vi è un processore Pentium.

•

La DDR (Double Data Rate) SRAM è una memoria che acquisisce o fornisce i dati sia

sul fronte di salita sia sul fronte di discesa del clock.

Si consideri ad esempio una DDR RAM che lavora con un clock di 133 MHz e con dati

da 8 bit; poiché questa memoria utilizza sia il fronte di salita sia il fronte di discesa del

clock, produce dati da 8 bit alla frequenza di 266 MHz.

In pratica la RAM lavora internamente dati da 16 bit e li consegna (preleva) in uscita

(in ingresso) 8 alla volta.

La memoria è organizzata internamente con 2 banchi separati. Un banco per gli

indirizzi pari, a cui si accede con il fronte di salita, e un banco per gli indirizzi dispari,

al quale si accede con il fronte di discesa del clock.

Le DDR hanno un tempo di accesso inferiore ai 10 ns, un tempo di vita inferiore alle

corrispondenti DDR DRAM e vengono utilizzate come cache.

•

La DP (Dual-Ported) RAM è una memoria in grado di eseguire contemporaneamente,

o quasi, operazioni di lettura e scrittura, a differenza delle altre RAM, che devono

essere rinominate come SP (Single-Ported) RAM, nelle quali è possibile un accesso

per volta.

Molti microprocessori implementano al loro interno proprio una DPRAM o una multiport

RAM.

In commercio le SRAM si trovano come componenti in logica sparsa oppure integrati

(embedded) in altri chip.

Le SRAM asincrone e sincrone in logica sparsa vengono utilizzate come:

• cache memory di primo e secondo livello;

• memorie nei sistemi di processo in tempo reale dei segnali digitali;

• buffer degli hard disk;

• memoria per trasferimento di pacchetti di dati (burst);

• a volte come memoria principale di un sistema a microprocessore.

Le SRAM embedded trovano applicazione nei seguenti casi:

• cache primaria interna ai microprocessori (da qualche KB fino a diversi MB);

• in FPGA e CPLD (qualche KB);

• nell’elettronica automobilistica;

• nell’elettronica di consumo (fotocamere, cellulari, ecc.).

La tecnologia di costruzione delle SRAM può essere bipolare (TTL, ECL) e unipolare

(NMOS e CMOS).

La tecnologia bipolare consente di avere dispositivi più veloci con tempi di pochi ns,

massimo 30 ns; il consumo di potenza è però piuttosto elevato.

La tecnologia unipolare invece è la più diffusa, dati i vantaggi dei MOS nei confronti dei BJT

per quanto riguarda la scala di integrazione e i consumi.

I tempi di accesso sono invece un po’ superiori e si arriva fino a un massimo di 70 ns.

Un esempio di SRAM di piccole dimensioni è la KM62256C Family della Samsung Electronics.

Si tratta di una memoria da 32 K × 8 in tecnologia CMOS a basso consumo.

Una SRAM di dimensioni più grandi è la 89LV1632 della Maxwell Technologies.

Si tratta di un integrato particolare perché del tipo MCM (Multi-Chip Module), costituito

da quattro moduli SRAM ciascuno da 512 K × 8 bit per una capacità totale di 16 Mbit.

L’integrato SRAM IS61LV25616AL della ISSI (Integrated Silicon Solution, Inc.) è

caratterizzato da una struttura a vettore di word e non a matrice; si nota infatti la presenza

di un decodificatore di riga ma non di colonna.

RAM dinamica

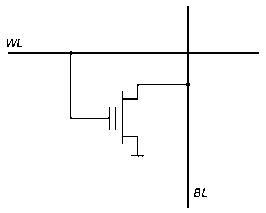

La RAM dinamica, nota anche come DRAM, è una memoria costituita da condensatori

ottenuti come elementi parassiti tra gate e substrato del MOS.

La capacità, che ha un valore di alcuni pF, occupa uno spazio decisamente inferiore al

flip-flop, che costituisce la cella elementare della SRAM.

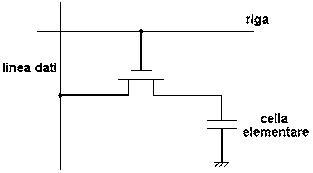

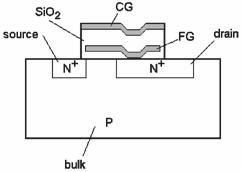

La cella elementare della DRAM (mostrata in figura)

è completata con un NMOS che collega il condensa-

-tore alla linea dati.

Se la linea di riga è a livello alto, il transistor NMOS

è saturo e il condensatore risulta collegato alla linea

dati.

È così possibile effettuare un’operazione di scrittura

di un bit 0 o 1 scaricando o caricando il condensatore

Attraverso la stessa linea di colonna si può anche

rilevare la tensione ai capi del condensatore per

l’operazione di rinfresco o di lettura.

Rispetto alla cella a dieci MOS della SRAM, in questo tipo di memoria lo spazio è decisamente

inferiore.

Infatti la scala di integrazione delle DRAM è di gran lunga superiore a quella della SRAM.

Orientativamente la capacità di integrazione delle DRAM è quattro volte superiore a quella

delle SRAM, mentre il costo per bit è circa cinque volte inferiore.

Ne consegue, inoltre, che anche la potenza assorbita da un condensatore è inferiore a quella

di un flip-flop.

La DRAM però è caratterizzata dalla necessità dell’operazione di rinfresco (refresh) delle celle

di memoria poiché i MOS, anche se sono spenti, non isolano perfettamente i condensatori

dalle linee.

Dopo poche decine di millisecondi la carica immagazzinata nei condensatori è completa-

-mente perduta.

L’attività di refresh, effettuata periodicamente all’incirca ogni 2 ms, prima cioè del decadi-

-mento completo della carica, rallenta le operazioni di lettura e scrittura in memoria.

Inoltre il refresh è necessario dopo ogni lettura poiché tale operazione ha carattere distrut-

-tivo per il condensatore.

In genere il circuito di refresh si trova a bordo della memoria, quindi la DRAM esegue

autonomamente l’operazione.

Da un punto di vista dell’operatore la memoria si presenta come una SRAM.

Un altro problema che si presenta nella DRAM è la variazione della carica dei condensatori

per effetto dei raggi cosmici.

Per tale motivo i microprocessori attivano un apposito programma, chiamato ECC (Error

Correction Code) che scansiona la memoria e corregge gli eventuali errori verificatesi.

Tale operazione non introduce ritardi nel funzionamento della memoria.

Le DRAM possono essere suddivise in due tipi di

categorie (vedi figura a lato) in funzione della

loro interfaccia con il mondo esterno.

La differenza tra DRAM classiche e DRAM sincrone

consiste nel buffer di interfaccia con il mondo

esterno alla memoria.

Le DRAM asincrone sono così chiamate perché il

loro funzionamento è completamente trasparente,

ovvero i dati vengono memorizzati o letti solo con

gli indirizzi e i segnali di controllo, senza necessità

di un segnale di clock.

Le DRAM sincrone invece necessitano per il loro

funzionamento del clock di sistema.

L’integrato MT48LC128M4A2 è una RAM dinamica

della Micron Technology ed è commercializzata in

versioni da 128 M, 64 M e 32 M.

Cella elementare di una DRAM

Classificazione delle DRAM.

Confronto tra SRAM e DRAM

La SRAM rispetto alla DRAM presenta i seguenti vantaggi:

• è più veloce;

• ha un consumo molto limitato (μW) quando è in standby;

• è più facile da controllare;

• gli indirizzi vengono dati tutti nello stesso istante e non multiplexati come nella DRAM;

• la struttura simmetrica, a circuito differenziale, di ogni cella di memoria consente di

rilevare più facilmente le più piccole differenze di tensione del segnale;

• i componenti più recenti presentano un fenomeno di data remanence meno marcato

perché sono costruiti con una tecnologia più sofisticata.

La SRAM presenta i seguenti svantaggi:

• è più costosa, in particolare ha un costo per bit superiore;

• ha una capacità più bassa perché ha una struttura interna meno densa;

• ha un ciclo di vita mediamente inferiore alla DRAM

ROM

Le ROM (Read Only Memory) sono memoria a sola

lettura, ad accesso casuale e non volatili.

Nella figura a lato è riportata una classificazione

delle ROM, che sono di tre tipi:

• ROM a maschera;

• ROM programmabili;

• ROM riprogrammabili.

Le ROM cancellabili e riprogrammabili possono essere di varie

tipologie.

Le caratteristiche principali di queste memorie sono:

•

la sicurezza nell’immagazzinamento dei dati, che non

possono essere cambiati né per cause accidentali né per

eventuali virus informatici;

•

la conservazione dei dati per tutto il tempo di vita dell’integrato.

La ROM viene impiegata in varie applicazioni:

•

nei PC per la memorizzazione del sistema operativo (BIOS);

•

per memorizzare tabelle di dati per svolgere velocemente

funzioni matematiche e logiche;

•

per memorizzare i caratteri font nelle schede video;

•

per la decodifica dei display alfanumerici;

•

come rete di transcodifica;

•

nell’elettronica di consumo;

•

embedded in FPGA e CPLD

Classificazione delle ROM.

ROM a maschera

La ROM a maschera è una memoria che contiene dati a carattere permanente, inseriti dal

costruttore in fase di realizzazione e pertanto non sono modificabili.

L’operazione di lettura consiste nel porre sugli ingressi un indirizzo e nel rilevare sulle

uscite il contenuto della locazione selezionata.

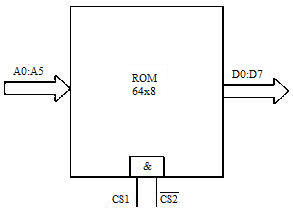

In figura a lato è riportato il simbolo logico di una

ROM 64 × 8.

La memoria è dotata di 6 linee di ingresso, quindi

contiene 64 word da 8 bit ciascuna.

Le uscite sono del tipo three-state oppure open-

-collector per permettere il collegamento a bus con

altri integrati.

Di solito l’integrato è provvisto di due ingressi di

abilitazione, di cui uno attivo a livello basso e

l’altro a livello alto .

Simbolo logico di una ROM 64 × 8

ROM programmabili

Le ROM programmabili sono memorie in cui i dati vengono inseriti dall’utente e non

dalla casa costruttrice.

Una ROM programmabile rispetto a una memoria a maschera (non programmabile)

possiede una maggiore flessibilità di impiego poiché consente all’utente di decidere e

immettere personalmente i dati da memorizzare.

È molto più conveniente economicamente rispetto a una ROM se è richiesta una quantità

limitata di integrati.

Esiste in commercio una grande varietà di ROM programmabili:

• ROM programmabili una sola volta e quindi non cancellabili;

• ROM programmabili e cancellabili più volte.

PROM (Programmable ROM)

Sono ROM programmabili in quanto costruttivamente molto simili alle Mask ROM costituite

da un decodificatore e da una matrice, a BJT o a MOS, completa di transistor in tutti gli

incroci tra le righe e colonne.

L’utente può inserire un bit 0 interrompendo il collegamento tra il transistor e la colonna.

Dalla figura a lato, si può osservare che alle righe

sono collegate le basi dei BJT, mentre alle colonne

gli emettitori tramite un fusibile.

In tale situazione tutti i bit contenuti nella matrice

sono 1.

Se, dopo aver selezionato una riga della matrice,

si fa circolare, in un BJT della riga attivata, una

corrente di elevata intensità tra collettore e

emettitore, si brucia il fusibile scollegando così

l’emettitore dalla colonna.

La tensione da applicare all’integrato per fondere

il fusibile, chiamata tensione di programmazione,

è di solito tra i 10 V e i 20 V.

Questa operazione produce l’effetto di inserire uno 0

nella cella di memoria desiderata.

È ovvio che il fusibile non può essere più ripristinato e pertanto la memoria non può

essere più modificata.

Al più è possibile inserire altri 0 facendo fondere altri fusibili.

Le modalità operative e le temporizzazioni di una PROM sono uguali a quelle delle ROM.

Matrice di una PROM a BJT

EPROM (Erasable PROM)

L’impossibilità di cancellare e riprogrammare la PROM ha portato alla realizzazione di una

ROM programmabile e cancellabile più volte.

La EPROM è una memoria a sola lettura programmabile e cancellabile, cioè è una ROM

programmabile direttamente dall’utente.

La cella di memoria di una EPROM (raffigurata nella

figura a lato), diversa dalle celle di una ROM e di una

PROM, si basa sul transistor FAMOS.

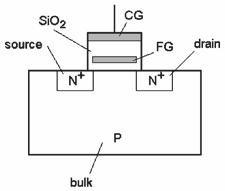

Il transistor FAMOS (Floating-gate Avalanche injection

MOS) ha la struttura di un MOS ma con due gate, come

illustrato anch’esso nella figura a lato.

Il MOS è dotato di due gate: un gate di controllo CG

(Control Gate), gate di cui sono provvisti tutti i MOS e

accessibile dall’esterno, e un gate fluttuante FG (Floating

Gate) imprigionato nello strato di biossido di silicio.

Il gate FG, posto in una posizione intermedia tra il gate CG

e canale, è costituito di silicio policristallino, quindi è un

materiale conduttore che può immagazzinare cariche elet-

-triche.

Questo tipo di cella di memoria viene chiamata SLC (Single

Level Cell) perché la lettura consiste nel rilevare la presenza

o meno di una carica sul FG.

Pertanto la cella memorizza solo un bit.

Se si applica una tensione elevata tra CG e drain, si ha una

polarizzazione inversa della giunzione che porta a una iniezione

di elettroni caldi.

Quando si riporta a zero la tensione tra CG e drain, diversi elettroni restano intrappolati

sul FG senza possibilità di transitare verso altre regioni, poiché il gate FG è perfettamente

isolato nel biossido di silicio.

Se si pone su CG una tensione per eseguire la lettura, il canale tra drain e source non ha

alcuna possibilità di formarsi.

Infatti la carica negativa sul FG alza la tensione di soglia del MOS che non può condurre e

tra drain e source il circuito resta aperto.

Per rimuovere la carica intrappolata, operazione che viene eseguita con l’esposizione ai

raggi UV, è necessario rendere conduttore, sia pure in modo debole, il biossido di silicio in

modo tale da permettere agli elettroni di migrare dalla loro posizione sul FG.

Con riferimento alla soprastante cella di memoria , se si attiva la word line WL, ponendo

una tensione su CG, si verificano due casi:

•

una carica è memorizzata sul FG, quindi tra drain e source non si è il canale.

Ne consegue che la bit line BL è isolata da massa quindi è collegata alla tensione di

alimentazione, ciò equivale a 1 logico;

•

non vi è carica memorizzata sul FG, quindi si forma il canale tra drain e source e la BL

è collegata a massa, che equivale allo 0 logico

Cella di memoria di una EPROM

Struttura di un FAMOS

Il tempo di acceso di questa memoria è dell’ordine di 100 ns.

L’operazione di scrittura, che si esegue applicando tensioni da 10 V a 20 V sia sul CG

(WL) sia sul drain (BL), richiede un tempo dell’ordine dei ms.

La carica immagazzinata nella cella tende con il tempo a migrare verso il canale ma

anche e soprattutto verso il CG.

Nonostante il fenomeno della perdita, la ritenzione della carica da parte della memoria

è minimo di 10 anni.

La programmazione può essere fatta anche per parti in fasi successive e necessita di

uno strumento chiamato programmatore di EPROM.

La programmazione può essere fatta anche da un PC con una opportuna interfaccia.

La cancellazione dei dati consiste nell’esporre la EPROM (che nella parte superiore è

provvista di una finestra trasparente) a una lampada a raggi UV per un tempo che

dipende dall’intensità dei raggi UV, in generale dai 10 ai 20 minuti.

Durante la cancellazione tutti i terminali sono posti a massa.

È buona norma, dopo la programmazione, oscurare la finestra della EPROM perché

l’esposizione alla luce solare e artificiale, può provocare accidentali cancellazioni.

L’esposizione della memoria alle radiazioni UV comporta danni alla struttura reticolare

per cui gli integrati hanno un’affidabilità garantita dal costruttore per un numero di

riprogrammazioni tra 100 e 1000.

Le EPROM vengono generalmente utilizzate nella costruzione di circuiti prototipi, sia

perché hanno un costo limitato sia per l’elevata capacità, e comunque in tutte quelle

applicazioni dove è necessario aggiornare il software.

Per quanto riguarda le temporizzazioni e le modalità operative, sono perfettamente

analoghe alle ROM e alle PROM della stessa versione.

L’operazione di programmazione è sempre seguita da una di lettura come verifica dei

dati immessi nella memoria.

Le EPROM presentano i seguenti inconvenienti:

•

devono essere rimosse dal circuito residente per effettuare le operazioni di

programmazione e di cancellazione;

•

nel caso di modifica anche solo parziale dei dati bisogna procedere alla cancellazione

di tutta la memoria;

•

i tempi di cancellazione possono essere piuttosto lunghi.

EEPROM o E²PROM (Electrically Erasable Programmable Read Only Memory)

A differenza delle EPROM, possono essere programmate e cancellate elettricamente

senza la necessità di essere rimosse dal circuito residente.

Un altro notevole risparmio di tempo è costituito dalla possibilità di poter cancellare

selettivamente ogni singolo byte.

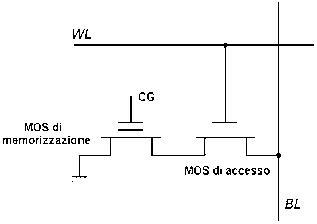

La cella della EEPROM, sempre del tipo SLC, è simile a quella della EPROM ma il transistor

di immagazzinamento della carica può essere di tre tipi differenti:

•

MNOS (Metal Nitride Oxide Silicon) e SONOS (Silicon Oxide Nitride Oxide Silicon);

•

FLOTOX (FLOating gate Thin OXide), tecnologia più diffusa;

•

TP-EEPROM (Textured Polysilicon EEPROM).

Tutti i tipi di transistor si basano sull’effetto tunnel FowlerNordheim che si verifica

quando un intenso campo elettrico (109 V/m) ai capi del biossido di silicio (SiO2)

altera la struttura a bande del silicio in modo tale da consentire la rimozione o l’iniezione

degli elettroni.

Nel transistor FLOTOX (mostratoa lato) il floating gate è

separato dal drain da uno spessore di SiO2 di 8-10 nm,

mentre nel FAMOS lo spessore è di 100 nm in modo tale

da massimizzare l’effetto tunnel.

I cicli di programmazione/cancellazione tendono a dan-

-neggiare la struttura del materiale, pertanto è preferibile

limitare l’intensità del campo elettrico e ridurre l’area

dello strato sottile di biossido nelle vicinanze del drain.

Oltre al transistor FLOTOX la cella (rappresentata

a lato) è costituita da un altro transistor che ha la

funzione di controllare l’accesso al bit memorizzato.

L’EEPROM presenta i seguenti inconvenienti:

•

l’area occupata da una cella FLOTOX è superiore

di 3-4 volte all’area della cella FAMOS, ne

consegue che le EEPROM sono meno dense

delle EPROM;

•

la modalità di programmazione è lenta e

complessa.

L’integrato TMS28C64 è una EEPROM 8K × 8.

Transistor FLOTOX.

Cella di memoria della EEPROM.

EAROM (Electrically Alterable ROM)

Sono memorie non volatili, cancellabili elettricamente in modo mirato, anche se costrut-

-tivamente sono complesse e diverse dalle altre memorie.

Sono poco utilizzate per i seguenti inconvenienti:

•

richiedono tempi di scrittura dell’ordine del millisecondo mentre per la lettura solo

di qualche microsecondo;

•

tecnologia complessa;

•

bassa densità;

•

tensioni di alimentazione elevate e multiple;

•

piedinatura non standard.

NVRAM (Non Volatile RAM)

Sono una categoria di memorie con struttura RAM che non perdono i dati quando si

toglie la tensione di alimentazione.

Sono costituite in generale da una RAM statica che per i bassi tempi di accesso

costituisce l’interfaccia con l’utente.

Per il mantenimento dei dati si può integrare sullo stesso chip:

•

una Shadow EEPROM (EEPROM ombra);

•

una batteria al litio.

La EEPROM serve a salvare i dati scritti nella RAM statica quando si toglie o viene meno

l’alimentazione.

La batteria al litio, che ha la stessa funzione della EEPROM, può essere integrata comple-

-tamente nel chip ovvero può essere integrata ma resa accessibile dall’utente in modo

da poter essere sostituita.

Sono memorie in disuso perché sono meno competitive delle memorie flash a causa dei

seguenti fattori:

•

bassa densità;

•

costo per bit elevato

Flash memory

Le memorie flash sono a lettura e scrittura; si possono considerare un tipo di EEPROM

perché sono costruite con lo stesso tipo di transistor a gate fluttuante.

Da un punto di vista operativo differiscono dalle EEPROM perché sono cancellabili elet-

-tricamente per gruppi di byte.

Banco di memoria

L’espansione di una memoria è una operazione che consiste nell’aumentare le dimensioni

della memoria per il numero di bit dei dati e/o per il numero dei dati stessi.

Questa operazione si esegue collegando assieme più integrati.

La necessità di mettere assieme più integrati deriva anche dal fatto che la memoria in

tutti i sistemi digitali deve servire sia per contenere dati permanenti (si pensi ad esempio

al sistema operativo) sia per contenere dati o programmi da elaborare (ad esempio il

programma applicativo).

In definitiva la memoria deve essere composta da una parte fissa (ROM) e da un’altra

parte a lettura e scrittura (RAM).

L’insieme di tutti gli integrati della stessa tipologia o di tipologia diversa prende il nome

di banco di memoria.

Espansione del numero di bit

L’espansione di una memoria per numero di bit consiste nell’aumentare il numero di

bit di ogni singolo dato.

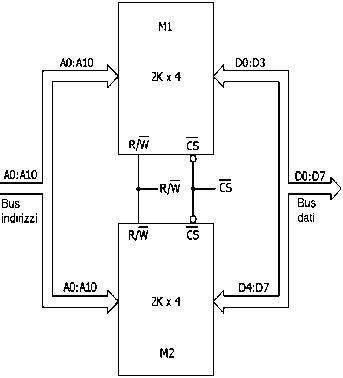

Ad esempio si vuole configurare una memoria di 2048 parole da 8 bit ciascuna avendo

a disposizione una ROM (o RAM è indifferente) di 2K × 4.

L’integrato, contenente 2048 parole da 4 bit ognuna, è dotato di 11 linee di indirizzo

A0 − A10 (poiché

= 2048), 4 linee di dati D0 − D3, una linea di (o solo read se

è una ROM) e un ingresso di abilitazione del chip al funzionamento CS.

L’insieme delle linee dei dati prende il nome di bus dei dati (data bus), mentre gli ingressi

d’indirizzo si definiscono bus degli indirizzi (address bus).

A differenza del bus indirizzi che è unidirezionale

(gli indirizzi sono ingressi di memoria), il bus

dati è unidirezionale nelle ROM ma bidirezio-

-nale nelle RAM.

Infatti il dato è un ingresso se deve essere

memorizzato, un’uscita se deve essere letto.

Sono necessari quindi due integrati di 2K×4

collegati in parallelo per fornire 2 K parole da

8 bit (come in figur a lato).

Le linee di e di sono comuni

allo scopo di attivare contemporaneame-

-nte i due integrati.

Uno stesso indirizzo posto in ingresso

seleziona la stessa locazione nelle due

memorie.

L’integrato M1 fornisce i 4 bit meno signifi-

-cativi del dato, ed M2 i 4 più significativi.

Espansione della memoria per numero di bit

Espansione del numero di dati

L’espansione del numero di dati di una memoria si ottiene con integrati che lavorano

alternativamente e non simultaneamente

come nel caso precedente; lo schema è

riportato a lato.

Se si dispone di due integrati della capacità

di 1K × 8 ciascuno, si può realizzare un

banco da 2K × 8.

Ogni integrato necessita di 10 linee

d’indirizzo A0 − A9 per selezionare

1024 dati . Un ulteriore

ingresso d’indirizzo A10 collegato al ,

consente di abilitare al funzionamento un

integrato alla volta.

Con

si abilita il chip M1, che fornisce

in uscita i primi 1024 byte, mentre con

si abilita il chip M2, che invia in uscita gli altri

1024 dati.

La porta NOT svolge la funzione di decodifica-

-tore delle due memorie.

Dalla figura si può osservare che le linee dati

di ugual peso sono collegati tra loro; questo tipo di collegamento è realizzato di solito con

uscite di tipo tri-state.

Riassumendo si può affermare che la memoria M1 è selezionata dai seguenti bit di

indirizzo , che vanno da

Con gli indirizzi , da , si selezionano le celle della memoria M2.

Espansione della memoria per numero di dati

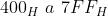

Espansione composta e mappatura di un banco di memoria

Se si dispone di integrati da 1K × 4 e si vuole progettare un banco di memoria da 3K × 8,

si deve espandere sia per numero di bit che per numero di byte.

Con due integrati, funzionanti in parallelo cioè con il in comune, si ottiene una

memoria con capacità di 1K × 8; sono quindi necessari sei integrati organizzati in tre

coppie disposte in serie, come indicato nella sottostante figura.

Gli ingressi d’indirizzo devono essere comuni a tutti i chip per la selezione delle locazioni

di memoria, mentre per abilitare una sola coppia di integrati, tramite le linee di

attive

a livello basso, sono necessari due ulteriori ingressi d’indirizzo A10 e A11.

La tabella della funzione per la progettazione della rete di decodifica è riportata in

figura (b).

Può risultare conveniente sostituire la rete di decodifica con un solo integrato: un

decodificatore, ad esempio il 74138.

Con l’uso di un integrato vi è la possibilità di espandere ulteriormente l’area di memoria

ed eliminare il problema della progettazione.

Per mappare la memoria, cioè definire gli indirizzi di inizio e di fine di ciascuna coppia di

integrati, si costruisce la tabella (c) disponendo gli ingressi d’indirizzo secondo il proprio

peso.

I primi 10 bit degli indirizzi da , comuni a tutti, servono a selezionare le locazioni

interne a ogni coppia di integrati.

La prima locazione ha indirizzo 00…0, l’ultima ha indirizzo 11…1.

I due bit più significativi decodificano le coppie di memorie: 00 per M1,

01 per M2 e 10 per M3; la configurazione 11 potrebbe servire a espandere

ulteriormente l’area di memoria.

Ciascuna configurazione viene tradotta in esadecimale per una più facile interpretazione.

Lorem Ipsum Dolor

Cupidatat excepteur ea dolore sed in adipisicing id? Nulla lorem deserunt aliquip officia reprehenderit fugiat, dolor excepteur in et officia ex sunt ut, nulla consequat. Laboris, lorem excepteur qui labore magna enim ipsum adipisicing ut. Sint in veniam minim dolore consectetur enim deserunt mollit deserunt ullamco. Mollit aliqua enim pariatur excepteur. Labore nulla sunt, in, excepteur reprehenderit lorem fugiat. Ipsum velit sunt! Non veniam ullamco amet officia ut, ex mollit excepteur exercitation fugiat eu ut esse cupidatat in velit. Non eu ullamco in pariatur nisi voluptate mollit quis sed voluptate ea amet proident dolore elit. Occaecat nostrud dolore sunt, ullamco eu ad minim excepteur minim fugiat. Nostrud culpa eiusmod dolor tempor et qui mollit deserunt irure ex tempor ut dolore. Dolore, nostrud duis ad. In nulla dolore incididunt, sit, labore culpa officia consectetur mollit cupidatat exercitation eu. Aute incididunt ullamco nisi ut lorem mollit dolore, enim reprehenderit est laborum ut et elit culpa nulla. Excepteur fugiat, laboris est dolore elit. In velit lorem id, et, voluptate incididunt ut ad in sunt fugiat, esse lorem. Nisi dolore ea officia amet cillum officia incididunt magna nisi minim do fugiat ut nostrud dolore Qui in est in adipisicing ea fugiat aliqua. Reprehenderit excepteur laboris pariatur officia sit amet culpa aliquip quis elit eiusmod minim. Sint ut ut, proident in mollit do qui eu. Pariatur et cupidatat esse in incididunt magna amet sint sit ad, sunt cillum nulla sit, officia qui. Tempor, velit est cillum sit elit sed sint, sunt veniam.

© Irure ut pariatur ad ea in ut in et. In incididunt sed tempor