Dove saranno gli occhi tuoi quando si chiuderanno i miei

ELETTRONICA DIGITALE

… studiare, studiare ed ancora studiare,

è il solo modo di capire quanto possa

essere grande sia la propria ignoranza!

LATCH E FLIP-FLOP

I latch e i flip-flop (FF) sono circuiti logici che hanno alcune carat-

teristiche comuni:

•

sono circuiti bistabili, ovvero circuiti la cui uscita può esistere

solo in due stati stabili (livello basso e livello alto);

per far avvenire la transizione da uno stato all’altro è necessario

un segnale di eccitazione in ingresso cioè il circuito cambia

stato solo se si dà un segnale di eccitazione;

•

il circuito perde il contenuto se si toglie l’alimentazione;

•

sono circuiti sequenziali poiché le loro uscite dipendono sia dagli

ingressi, sia dalla loro storia precedente;

•

sono celle di memoria da un bit; lo stato del circuito è il livello

logico in cui si trova l’uscita Q, che può essere 0 oppure 1;

•

hanno due uscite ( ) che devono stare su stati logici

contrapposti;

•

il numero di ingressi può variare da un dispositivo all’altro.

I latch possono essere con o senza segnale di abilitazione (Enable).

I flip-flop invece possono essere di 3 tipi:

•

PET oppure NET; commutano in entrambi i casi su un fronte del clock; i PET (Positive

Edge Triggered) sul fronte positivo e i NET (Negative Edge Triggered) sul

fronte negativo;

•

pulse triggered; necessitano di un impulso completo per commutare;

•

data lock-out; sono simili ai pulse triggered, ma hanno un ingresso di clock dinamico che

disabilita gli ingressi dei dati dopo il fronte di salita dell’impulso di clock.

Latch SR

Il latch può essere realizzato con porte NOR oppure NAND e in entrambi i casi le porte sono

collegate tra loro con la retroazione.

Latch SR a porte NOR

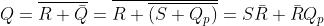

Il circuito di figura a lato rappresenta un

latch SR a porte NOR.

I due ingressi prendono il nome di Set (S)

e di Reset (R). La funzione di questi due

ingressi è di settare e di resettare l’uscita.

Settare vuol dire porre Q a 1, resettare vuol

Latch SR a porte NOR: schema circuitale (a), simbolo logico

(b), tabella degli stati estesa (c), tabella degli stati semplificata

dire porre Q a 0.

Questi due ingressi sono chiamati asin-

-croni perché controllano direttamente

le uscite senza la necessità di un segnale

di abilitazione.

Tutto il circuito ha un comportamento

asincrono o trasparente.

In figura (b) è riportato il simbolo logico.

Per verificare il funzionamento del circuito

è sufficiente applicare le configurazioni

agli ingressi riportate nella figura ( c).

Con Q è stato indicato lo stato attuale

dell’uscita e con Qp lo stato precedente.

Il funzionamento del latch in base al

valore logico assunto dagli ingressi è

il seguente.

•

S = R = 0: il latch resta bloccato nello stato precedente; se Qp = 0 la porta NOR A dà in

uscita 1, quindi tutto resta bloccato; analogamente si verifica se Qp = 1;

•

S = 0, R = 1: il latch si porta nello stato Q = 0, qualunque sia lo stato precedente perché

l’uscita della porta NOR B è comunque 0;

•

S = 1, R = 0: produce una Q = 1 indipendentemente dallo stato precedente, infatti

l’uscita della porta NOR A è comunque Q = 0;

•

S = 1, R = 1: è una configurazione vietata perché entrambe le uscite sono forzate

sullo stesso livello e questo non è accettabile; inoltre rimossi i livelli logici degli

ingressi, è imprevedibile lo stato in cui si porterà il circuito.

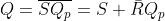

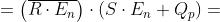

L’equazione caratteristica, che si evince sia dal circuito come uscita della porta NOR

B, sia dalla tabella (senza utilizzare le condizioni di indifferenza), è la seguente:

La tabella degli stati si può scrivere in modo più breve come indicato in tabella (d).

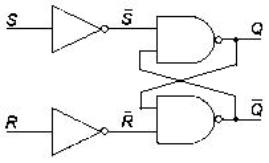

Latch SR a porte NAND

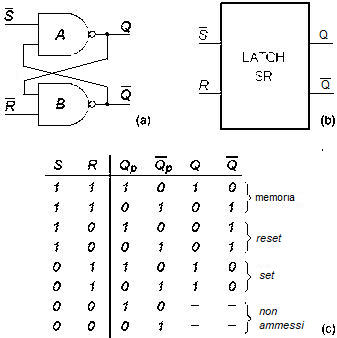

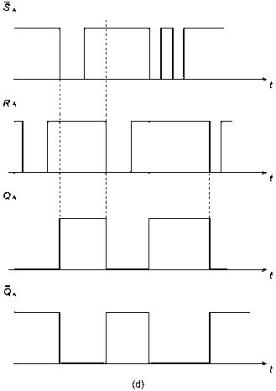

Il latch a porte NAND viene rappresentato

nelle figure (a) e (b); in figura ( c) si trova

la tabella degli stati.

Il comportamento di questo circuito è simile

a quello a porte NOR ma in questo caso gli

ingressi sono attivi a livello basso: infatti

Set e Reset sono rappresentati in modo negato

.

L’equazione caratteristica, che si può

ricavare sia dal circuito (come uscita della porta

NAND A), sia dalla tabella, è la seguente:

Latch SR a porte NAND: schema circuitale (a),

simbolo logico (b), tabella degli stati estesa (c),

cronogramma del latch a porte NAND (d)

Il funzionamento del latch SR può essere

analizzato anche con un diagramma temporale

come quello rappresentato in figura (d).

È possibile ottenere un SR a porte NAND con

ingressi attivi a livello alto, quindi con una

tabella identica a quella con porte NOR,

inserendo porte NOT, come indicato nella

sottostante figura

Latch SR a porte NAND con ingressi attivi a livello alto

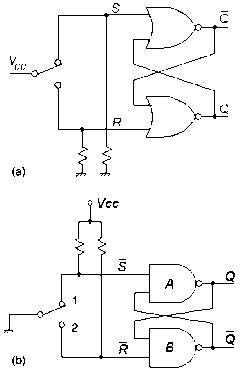

Interruttore antirimbalzo

Si analizza un’applicazione del latch come interruttore antirimbalzo (debouncer).

Come è noto, quando si aziona un interruttore si genera una serie di oscillazioni della

tensione, prima di stabilizzarsi definitivamente ad un valore preciso, che si traducono in

una successione di 0 e 1.

Per ovviare a questo inconveniente si può usare un latch

SR come interruttore antirimbalzo.

nella figura (a) a lato, viene proposto un latch a porte NOR

e in figura (b), un latch a porte NAND.

Con riferimento alla figura (b), si può osservare quanto

segue:

•

quando il contatto dell’interruttore è nella posizione

indicata con 1 (figura (b) si ha e quindi

l’uscita è Q = 1;

•

quando il contatto dell’interruttore è nella posizione

indicata con 2 si ha e quindi l’uscita è Q=0;

•

quando il contatto si porta dalla posizione 1 alla 2 si ha

, configurazione che lascia il latch bloccato

nello stato precedente.

Latch SR usato come interruttore antirimbalzo:

versione a NOR (a) e a NAND (b)

Si evince da quanto detto che eventuali rimbalzi del contatto sulla posizione 2, che

portano alternativamente gli ingressi del latch dalla configurazione alla

configurazione , non modificano lo stato in cui si trova il latch e pertanto

l’uscita Q non cambia. Questo si traduce con un passaggio netto di Q da 1 a 0

senza oscillazioni sul segnale

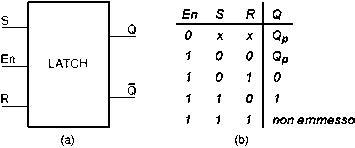

Latch SR sincrono con ingresso di abilitazione

A differenza dei latch asincroni, nei quali gli ingressi controllano direttamente le

uscite, in questo tipo di circuito gli ingressi controllano le uscite solo in presenza di un

segnale di abilitazione, Enable (En).

Un latch con ingresso di abilitazione si

definisce sincrono.

In figura a lato è rappresentato il simbolo

logico.

Se En non è attivo, un eventuale cambia-

-mento degli ingressi non influenza l’uscita,

come indicato nella figura (b)

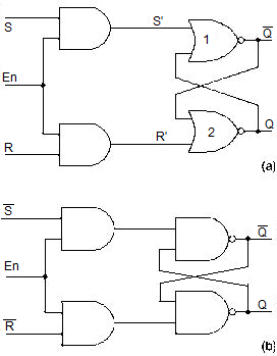

Nella figura (a) a destra è rappresentato un latch a

porte NOR con ingresso di abilitazione e in figura (b)

un latch a porte NAND con ingresso di abilitazione:

si nota come in entrambi i casi sia sufficiente aggiu-

-ngere due porte AND.

Il funzionamento del latch di figura (a) può essere

riassunto come segue:

•

En = 0; le uscite delle due porte AND valgono 0,

pertanto il latch rimane bloccato nello stato

precedente;

•

En = 1; le uscite delle due porte AND copiano i

segnali S e R, quindi il funzionamento segue

quanto indicato nella soprastante tabella (b).

Latch SR con ingresso di abilitazione:

simbolo logico (a), tabella degli stati (b).

Latch SR con ingresso di abilitazione:

realizzato a porte NOR (a) e a porte NAND (b).

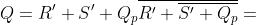

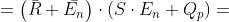

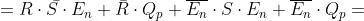

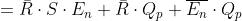

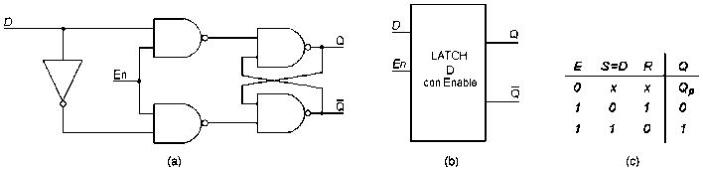

L’equazione caratteristica di questocircuito si

ottiene nel seguente modo:

dove l’ultimo passaggio è reso lecito dal fatto che sempre.

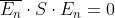

Latch D sincrono con ingresso di abilitazione

Il latch di tipo D, il cui circuito è rappresentato nella sottostante figura.

in

Questo è ottenuto collegando l’ingresso S a R tramite una porta NOT.

In figura (b) è riportato il simbolo logico.

La tabella che ne regola il funzionamento è derivata da quella del latch SR sincrono con

ingresso di abilitazione, sopprimendo le configurazioni in cui S e R sono uguali.

Si ottiene così la soprastante tabella ( c).

Il nome D deriva dalla considerazione che l’uscita copia l’ingresso D (data), in presenza del

segnale di abilitazione attivo, e quindi si tratta di un circuito che memorizza il dato posto

in ingresso.

L’equazione caratteristica di questo circuito si può ricavare da quella del latch SR tenendo

presente che

Latch D: schema circuitale (a), simbolo logico (b), tabella degli stati (c)

Il problema della corsa critica

Nei latch e nei flip-flop il fenomeno della trasparenza può causare problemi di instabilità e

di errato funzionamento.

Per effetto del fenomeno della trasparenza quando un segnale di uscita, tornando in

ingresso, trova il segnale di abilitazione ancora attivo, causa un’ulteriore commutazione,

naturalmente indesiderata, del circuito.

Tale commutazione può essere dovuta non solo ai nuovi ingressi ma anche alla presenza

di disturbi.

Un esempio tipico di race around si verifica nel latch JK,

di cui si riporta a lato lo schema.

Si ipotizzi di dare in ingresso la configurazione J=1, K=1

e che il ritardo di propagazione (Propagation Delay)

sia inferiore alla durata T dell’ingresso di abilitazione.

Le nuove uscite, tornando in ingresso, trovano l’enable

attivo e quindi generano nuove uscite che tornano in

ingresso e così via. Tutto ciò porta a una corsa continua

del circuito fino a quando si disattiva l’enable.

In queste condizioni non si è in grado di stabilire con certezza quale potrà essere lo stato

dell’uscita.

Tale problema si può evitare imponendo la condizione che , cosa che in pratica

risulta assai difficile da realizzare perché , nei circuiti integrati, è dell’ordine di pochi

nanosecondi.

Tuttavia la durata dell’abilitazione non può essere nemmeno troppo breve, perché il circuito

necessita di un tempo minimo per accettare i dati d’ingresso.

La soluzione al problema è stata trovata progettando dispositivi che commutano non su un

livello, ma solo su un fronte di transizione dell’enable: da livello alto al livello basso ovvero

da quello basso a quello alto.

Questi dispositivi si definiscono sincronizzati con un segnale di clock, cioè con un segnale

che commuta con una certa frequenza.

Il loro funzionamento è scandito dal fronte di commutazione del clock .

Latch JK: schema circuitale.

Flip-flop comandati su un fronte di clock

I flip-flop, noti anche come bistabili, sono circuiti sincronizzati, poiché l’acquisizione

dei dati d’ingresso avviene soltanto sul fronte del clock (edge triggered).

Pertanto gli ingressi dati (S e R, D, J e K, T) vengono definiti ingressi sincroni.

I flip-flop possono essere PET (Positive Edge Triggered) se commutano sul fronte di salita

(o positivo) del clock oppure NET (Negative Edge Triggered) se commutano sul fronte di

discesa (negativo) del clock.

Nel simbolo logico del PET la commutazione sul

fronte di salita è indicato con un piccolo triangolo

(chiamato Dynamic Input Indicator).

La presenza anche di un cerchietto indica invece

un flip-flop di tipo NET (figura (b)).

Generalmentei flip-flop sono dotati anche di

ingressi asincroni ovvero di ingressi che agiscono

direttamente sull’uscita indipendentemente dalla

presenza del segnale di clock.

Vengono indicati dai costruttori come preset (PRE)

e clear (CLR) e sono nella maggioranza dei casi

attivi a livello basso.

Il preset serve a settare l’uscita (Q = 1) mentre

il clear a resettarla (Q = 0).

Naturalmente i due ingressi asincroni non

devono essere attivati contemporaneamente.

Per la loro posizione nel simbolo logico si vedano,

ad esempio, le figure a lato (a), (b) e ( c).

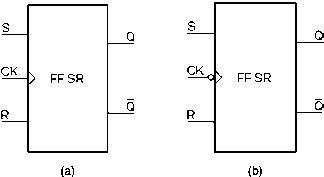

Flip-flop SR edge triggered: positive edge

triggered (a), negative edge triggered (b)

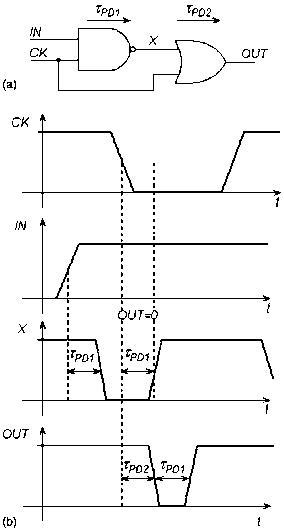

Circuito rivelatore del fronte di discesa del

clock (a) e relativi diagrammi temporali (b)

Tecnica della commutazione sul fronte di clock

Le soluzioni circuitali adottate per far avvenire la

commutazione sul fronte del clock possono essere

differenti e dipendono anche dalla famiglia logica

implementata, se TTL o CMOS.

Le soluzioni in genere si basano su tre concetti

diversi:

• generazione di impulsi stretti;

• immagazzinamento capacitivo;

• collegamento in cascata/parallelo dei latch.

Generazione di impulsi stretti

Un generatore di impulsi stretti è un multivibratore monostabile, in grado di generare

impulsi basandosi sul ritardo di propagazione delle porte logiche.

La tecnica della commutazione su un fronte di clock è ottenuta generando un impulso di

breve durata con un circuito posto sulla linea del clock.

Proprio la breve durata dell’impulso assicura da un lato il funzionamento del flip-flop e

dall’altro l’impossibilità del verificarsi della corsa critica.

Nella soprastante figura (a) è riportato un esempio di circuito che genera un impulso sul

fronte di discesa del clock e in figura (b) il relativo diagramma temporale.

Indicando con il ritardo di propagazione della porta NAND (figura (b)) e con il

ritardo della porta OR, si ipotizzi di portare l’ingresso IN a livello 1 nell’istante t*, mentre

il clock è sempre a livello alto.

Dopo il ritardo l’uscita della porta NAND si porta a livello 0.

Se si invia un impulso negativo sulla linea del clock, l’uscita della porta NAND, che era a 0,

si porterà a 1 dopo il tempo .

Ma in questo intervallo di tempo gli ingressi della porta OR sono entrambi a 0 e questo

porta anche l’uscita a 0 dopo il tempo .

Quando l’uscita della porta NAND commuta a 1 anche la porta OR commuta a 1.

L’impulso generato è largo il tempo sufficiente per abilitare il flip-flop, ma molto

stretto perché si possa verificare la corsa critica.

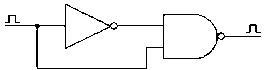

Un circuito analogo è quello rappresentato nella figura a

destra, il quale genera un impulso stretto basandosi sul

ritardo di propagazione della porta NOT.

Infatti la porta AND genera un segnale breve a livello

alto perché la porta NOT non ha ancora provveduto al

cambiamento della sua uscita.

Indicando stavolta con il ritardo della porta NOT e con quello della porta AND,

l’impulso risulta avere una durata pari a , ma con un ritardo pari a .

Circuito rivelatore del fronte

di salita del clock

Immagazzinamento capacitivo

Una tecnica che viene sovente usata nei TTL per la realizzazione di flip-flop comandati su

un fronte di clock è quella a immagazzinamento capacitivo.

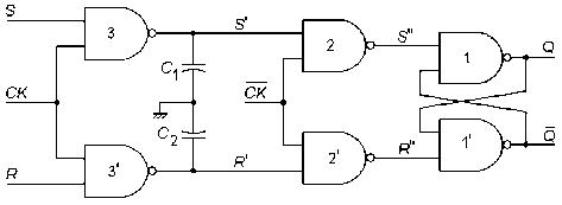

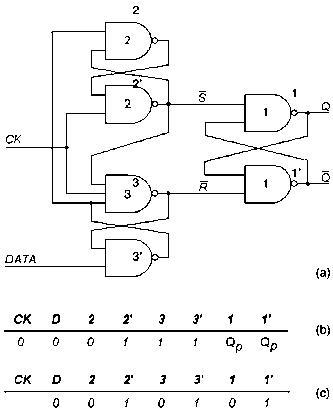

Si consideri il flip-flop SR comandato sul fronte di discesa del clock mostato nella figura

sottostante.

Se il clock è a 0, le porte 3 e 3′ sono disabilitate e quindi S′=R′=0; ne consegue che i due

condensatori C1 e C2 sono scarichi.

Le uscite delle porte 2 e 2′ sono a livello 1 e perciò il flip-flop 1-1′ è bloccato nello stato

precedente.

Sempre con CK=0 supponiamo che sia S=1 e R=0, quindi S′ e R′ saranno stabili a livello 0.

Quando il clock passerà a 1 risulterà S′=1 e R′=0 e ciò consentirà al condensatore C1 di

caricarsi, mentre il condensatore C2 resterà scarico.

Essendo CK=0, S″=R″=1 e il flip-flop 1-1′ resterà bloccato.

Con il ritorno del clock a 0 anche S′ andrà a 0 (R′ è già a 0) ma dato che C1 è carico, S′

resterà ancora a livello 1.

L’uscita della porta 2 si porterà a 0, ottenendo così il risultato di settare il flip-flop 1-1′.

Flip-flop SR comandato sul fronte di discesa del clock: immagazzinamento capacitivo

Collegamento cascata/parallelo dei latch

Si prenda in esame il flip-flop D mostrato a destra

che commuta sul fronte positivo del clock.

Si supponga che la situazione iniziale sia CK=0 e

D=0; risulterà allora la situazione riassunta nella

tabella (b).

Se successivamente il clock si porta a livello 1

cambia soltanto l’uscita della porta 3, che passa

a livello 0. Il flip-flop 1-1′ verrà di conseguenza

resettato e la situazione si presenterà come rias-

-sunto nella tabella ( c). Con il clock stabilmente

a livello 1, ponendo un 1 sull’ingresso D, le uscite

delle porte 2, 2′, 3 e 3′ non cambiano.

Analogamente si possono verificare tutte le altre

condizioni.

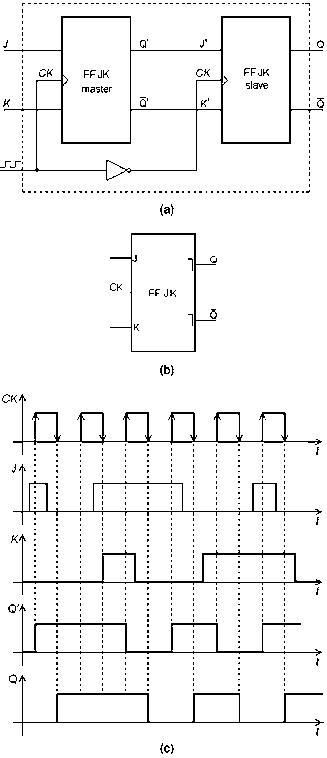

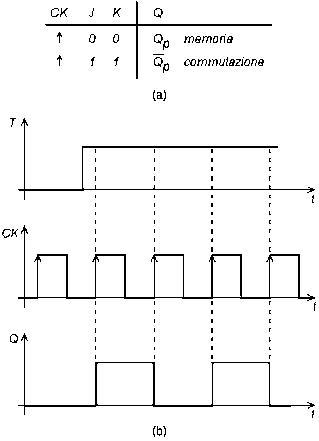

Flip-flop pulse triggered

I flip-flop pulse triggered sono così chiamati

perché necessitano dell’intero impulso

di clock per trasferire il dato in uscita.

Sono costruiti collegando in cascata due

flipflop identici che commutano uno sul fronte

positivo (flipflop master) e l’altro sul fronte

negativo (flip-flop slave) del clock (figura (a)

mostrata a lato).

In pratica allo slave il clock giunge complementato

rispetto al master. Tale connessione permette di

rendere indipendente la lettura dei dati in ingresso

dalla acquisizione degli stessi in uscita.

Inoltre è completamente risolto il problema della

corsa critica.

In questo tipo di flip-flop gli ingressi devono es-

-sere settati prima dell’arrivo del fronte di salita

del clock e devono essere stabili per tutto il

periodo in cui il master è abilitato.

Durante il fronte di salita del clock, il primo

master è abilitato alla commutazione mentre lo

slave è disabilitato.

Quindi il dato di ingresso su J viene trasferito su

Q′ ma non è ancora disponibile sull’uscita Q.

Gli ingressi devono essere settati prima dell’arrivo

del fronte di salita del clock e devono essere

stabili per tutto il tempo durante il quale il

clock è a livello alto.

Diversamente il master, ancora abilitato, potrebbe

catturare ingressi differenti e trasferirli erronea-

-mente in uscita. Durante il fronte di discesa del

clock (salita di CK) il primo flip-flop è disabilitato

mentre è abilitato lo slave: il dato viene trasferito

da J′ su Q.

Si consideri come esempio di funzionamento il diagramma

temporale di un flip-flop JK master-slave della figura (c ) a lato . Nel simbolo logico del

master-slave, riportato in figura (b) scompare il triangolo sull’ingresso di clock come

indicatore di ingresso dinamico ma vi è un simbolo di uscita posposto.

Flip-flop D comandato sul fronte di salita del clock:

realizzazione circuitale con collegamento cascata/

parallelo di latch (a), tabella della prima transizio-

-ne (b), tabella della seconda transizione (c).

Flip-flop JK master-slave:

schema logico (a), simbolo logico (b),

diagramma temporale (c).

I flip-flop master-slave sono poco utilizzati nelle applicazioni perché sono lenti.

Infatti l’acquisizione definita del dato si ha dopo l’intero impulso di clock.

Se è importante il fattore velocità sono preferiti gli edge triggered.

In tutte le altre applicazioni, come per esempio i registri, sono utilizzati invece i data

lock-out.

I flip-flop mastre-slave che si trovano in commercio sono di tre tipi: SR, JK e D.

Flip-flop data lock-out

Il flip-flop data lock-out è molto simile al master-slave tranne che per

l’ingresso di clock dinamico.

Il clock disabilita (lock-out) i dati dopo il fronte di salita, pertanto

non è necessario tenere gli ingressi stabili per tutta la durata

dell’impulso a livello alto.

In pratica il master è abilitato solo sul fronte di salita e disattivato

subito.

Lo slave è abilitato dopo il fronte di discesa del clock. Nel simbolo

logico, disegnato a destra, vi sono i simboli dynamic input indicator

e postponed output.

Flip-flop data lock-out:

simbolo logico

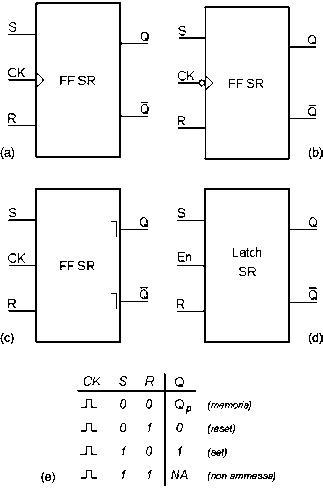

Flip-flop SR

Il flip-flop SR si trova in commercio temporizzato

con ingresso di abilitazione, con edge triggered

e con data lockout.

Indipendentemente dalla temporizzazione e dal

tipo di temporizzazione, il funzionamento è

descritto dalla tabella del latch SR, che viene qui

riproposta per i flip-flop SR temporizzati

(figura (e) mostrata a lato).

I simboli logici delle varie versioni sono riportate

nelle sottostanti figure (a), (b), ( c) e (d).

Il flip-flop SR viene utilizzato in molte applicazioni

quali celle di memoria, registri e contatori.

Simboli logici dei flip-flop SR positive edge triggered :

(a), flip-flop SR negative edge triggered (b), flip-flop

SR master-slave (c), latch SR con enable (d) e relativa

tabella degli stati (e).

Simboli logici dei flip-flop D positive edge triggered (a), flip-flop D negative edge triggered (b),

flip-flop D data lock-out (c) e relativa tabella degli stati (d).

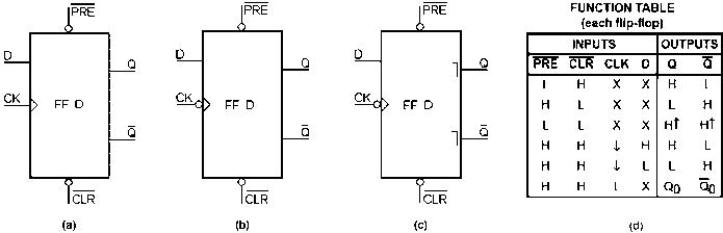

Flip-flop D

l flip-flop D (mostrati nelle sottostanti figure a), b), c) ) si trova in commercio temporizzato

con ingresso di abilitazione, con edge triggered e con data lock-out.

Analogamente al latch D, con il quale ha in comune la tabella degli stati, il flip-flop D è

ricavato dal flip-flop SR collegando l’ingresso S a R con una porta NOT.

La tabella è indicata in figura d).

Il campo applicativo del flip-flop D è quello tipico delle memorie: cella di memoria e

registri.

Viene utilizzato anche come elemento di ritardo di un segnale, D sta anche per delay.

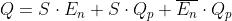

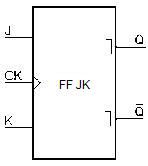

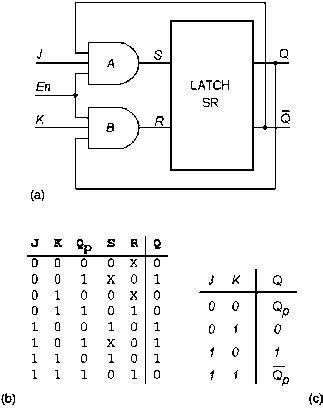

Flip-flop JK

Il flip-flop JK è stato realizzato per superare l’impossibilità del flip-flop SR nell’accettare la

configurazione non ammessa SR = 11.

Si costruisce a partire dal latch SR con una rete combinatoria che, valutando le uscite

precedenti , ecciti gli ingressi in modo tale da generare livelli logici complementati.

Il circuito combinatorio ha come ingressi J, K, Qp, Qp e come uscite S, R.

Dunque il nuovo flipflop con ingressi JK = 11, assume in uscita uno stato opposto rispetto

a quello precedente.

In figura a destra (b) è riportata la tabella degli

stati del nuovo flip-flop.

Se la configurazione di ingresso è JK = 00 con lo

stato precedente Q = 0, l’uscita del flip-flop JK deve

essere Qa = Qp = 0.

Pertanto, per ottenere tale uscita, il flip-flop SR può

essere eccitato con S=0, R=0 oppure con S=0,

R=1.

R può assumere quindi qualsiasi valore

indicato nella tabella con X.

Si possono verificare facilmente le altre configura-

-zioni.

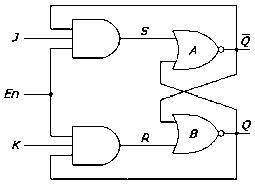

Dalla tabella di figura (b) si ricavano le seguenti

espressioni semplificate:

Se si vuole tener conto anche del segnale di

abilitazione E, le espressioni diventano:

Nella soprastante figurA (A) è disegnato lo schema circuitale e in figura (c ) la tabella

degli stati.

Il flip-flop JK è utilizzato nell’implementazione dei contatori.

Flip-flop JK con ingresso di abilitazione:

schema circuitale (a), tabella della verità

della rete di eccitazione (b),

tabella degli stati (c)

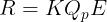

Flip-flop T

Il T (toggle) si ottiene collegando J con K.

Per ricavare la tabella si considera la soprastante

tabella (c ) del flip-flop JK e si eliminano le confi-

-gurazioni nelle quali J e K sono diversi.

Si ha così la tabella (a) del flip-flop T mostrata lato.

Poiché il flip-flop T non esiste in commercio, ma si

ricava dal JK, si può avere con qualsiasi tipo di

temporizzazione.

Osservando la tabella si nota che con T = 0 il flip-flop

resta bloccato nella sua posizione precedente, mentre

con T = 1 commuta l’uscita precedente.

Questo flip-flop è utilizzato come contatore con

modulo M = 2, infatti conta 0 e 1; ovviamente per

avere un conteggio maggiore sono necessari altri

flip-flop T.

Il flip-flop T è utilizzato anche come divisore di

frequenza, infatti esaminando il diagramma tempo-

-rale di figura (b) si deduce che la frequenza della

uscita Q è la metà della frequenza di clock.

Tabella degli stati di un flip-flop T (a) e

diagramma temporale (b)

Ingressi asincroni

Un problema che si presenta spesso nei flip-flop, e in generale in tutti i circuiti sequenziali,

è quello della inizializzazione del circuito, ovvero dello stato iniziale del funzionamento.

Tale problema (che si pone per tutti i circuiti in logica temporizzata) è importante perché

bisogna conoscere con certezza le condizioni iniziali del circuito, in modo da seguirne con

sicurezza l’evolversi degli stati.

Per risolvere tale problema ci sono gli ingressi asincroni.

In tutti i flipflop sincroni esistono due tipi di ingressi: sincroni e asincroni.

Gli ingressi sincroni (J e K nel flip-flop JK, D nel flipflop D, S e R nel flip-flop SR) sono

ingressi che necessitano della presenza del clock per cambiare lo stato dell’uscita.

Gli ingressi asincroni, indicati con PRE (preset) e CLR (clear), servono rispettivamente per

settare (Q = 1) e resettare (Q = 0) l’uscita e agiscono indipendentemente dal clock.

Il preset e il clear non possono essere attivati contemporaneamente, anche perché

ciò potrebbe danneggiare l’integrato.

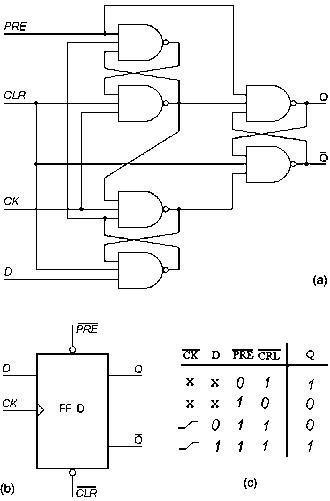

A titolo di esempio si riporta, nella figura (a) a lato,

un flip-flop D che commuta sul fronte d’onda

positivo con gli ingressi di Preset e Clear attivi a

livello basso.

Gli ingressi asincroni precedono gli ingressi dati e

il clock agisce direttamente sulle porte logiche di

uscita.

Nel simbolo logico ,mostrato infigura (b), i cer-

-chietti agli ingressi preset e clear indicano che i

livelli attivi sono quelli bassi.

Dalla tabella degli stati (figura ( c)) deduciamo

che, indipendentemente dagli ingressi CK e D, con

CLR = 1 (disattivo) e ingresso PRE = 0 (attivo),

l’uscita è Q = 1.

Con CK = X e D = X, PRE = 1 (disattivo) e

CLR = 0 (attivo), l’uscita è Q = 0.

Flip-flop D con comandi di preset e di clear:

schema circuitale (a), simbolo logico (b),

tabella degli stati (c).

Caratteristiche statiche e dinamiche

Sono qui elencate le principali caratteristiche elettriche e dinamiche dei latch e dei flip-flop

fornite dai costruttori con i datasheet.

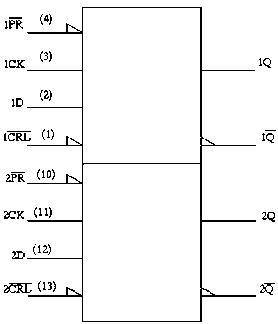

È stato preso come esempio il circuito integrato 7474.

L’integrato TTL 7474 contiene due flip-flop tipo D positive edge triggered, dotati di ingressi

di preset e clear.

Ogni flip-flop lavora singolarmente, cioè indipendente-

mente dall’altro. In figura a lato è riportato il simbolo

logico IEEE/ANSI e IEC.

Il simbolo logico racchiude due rettangoli, ognuno

rappresenta un flip-flop: quello superiore è contrad-

-distinto dal numero 1 (1PRE, 1 CLK 1D, 1CLR, 1Q e

1Q), quello inferiore dal 2 (2PRE, 2 CLK 2D, 2CLR, 2Q

e 2Q). La presenza di un triangolo, interno al simbolo,

sulla linea del clock sta a significare che il dispositivo

commuta sul fronte del clock.

L’assenza sulla stessa linea dell’altro triangolo esterno, in

sostituzione del cerchietto, segnala che il flip-flop è cadenzato sul fronte positivo del clock.

Gli ingressi di preset e clear sono attivi bassi, infatti sono soprassegnati e sulla loro linea

troviamo il triangolo di negazione.

Nell’interno del rettangolo vi sono le lettere S e R, iniziali delle operazioni asincrone Set e

Reset.

Simbolo logico IEEE/ANSI e IEC

del flip-flop D 7474

Caratteristiche statiche

Le principali caratteristiche statiche operative raccomandate dal costruttore sono le

seguenti:

• , high-level input voltage (minimo valore della tensione d’ingresso

a livello alto);

• , low-level input voltage (massimo valore della tensione d’ingresso a

livello basso);

• , high-level output current (massimo valore della corrente di uscita a

livello alto);

• , low-level output current (massimo valore della corrente di uscita a

livello basso);

• , high-level output voltage (tipico valore della tensione di uscita a

livello alto);

• , low-level output voltage (tipico valore della tensione di uscita a livello basso)

• , high-level input current (massimo valore della corrente d’ingresso a

livello basso);

• , low-level input current (massimo valore della corrente d’ingresso

a livello basso);

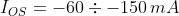

• , short-circuit output current (valore minimo e massimo della

corrente di uscita di corto circuito);

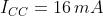

• , supply current (corrente di alimentazione).

Caratteristiche dinamiche

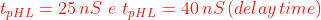

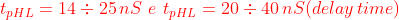

In questa sezione vengono presi in considerazione i tempi di commutazione; si definiscono:

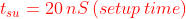

• : tempo di predisposizione; è l’intervallo di tempo precedente il

fronte attivo di commutazione durante il quale il dato, in sincronismo con il clock,

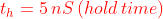

deve essere presente in ingresso;

• : tempo di mantenimento; è l’intervallo di tempo seguente il

fronte attivo di commutazione durante il quale il dato, in sincronismo con il clock,

deve permanere in ingresso;

• : ritardi di propagazione, sono gli

intervalli di tempo che intercorrono tra l’istante di attivazione del clock e l’istante

in cui l’uscita cambia stato;

• : ritardi di propagazione, sono gli intervalli di

tempo che intercorrono tra l’istante di attivazione degli ingressi asincroni e

l’istante in cui l’uscita cambia stato;

• : massima frequenza di funzionamento; è il valore massimo di

frequenza oltre il quale il costruttore non garantisce un corretto funzionamento

dell’integrato; nel caso del 7474 è evidente che la frequenza consigliabile è di 15

MHz poiché a 25 MHz non tutti gli integrati sarebbero affidabili;

• : durata dell’impulso; è il minimo intervallo di tempo di

permanenza del clock a livello alto prima di tornare basso;

• : durata dell’impulso; è il minimo intervallo di tempo di

permanenza del clock a livello basso prima di tornare alto;

• : durata dell’impulso; è il minimo intervallo di tempo di

permanenza degli ingressi asincroni a livello basso al fine di settare o resettare in

modo certo il flip-flop.

Lorem Ipsum Dolor

Cupidatat excepteur ea dolore sed in adipisicing id? Nulla lorem deserunt aliquip officia reprehenderit fugiat, dolor excepteur in et officia ex sunt ut, nulla consequat. Laboris, lorem excepteur qui labore magna enim ipsum adipisicing ut. Sint in veniam minim dolore consectetur enim deserunt mollit deserunt ullamco. Mollit aliqua enim pariatur excepteur. Labore nulla sunt, in, excepteur reprehenderit lorem fugiat. Ipsum velit sunt! Non veniam ullamco amet officia ut, ex mollit excepteur exercitation fugiat eu ut esse cupidatat in velit. Non eu ullamco in pariatur nisi voluptate mollit quis sed voluptate ea amet proident dolore elit. Occaecat nostrud dolore sunt, ullamco eu ad minim excepteur minim fugiat. Nostrud culpa eiusmod dolor tempor et qui mollit deserunt irure ex tempor ut dolore. Dolore, nostrud duis ad. In nulla dolore incididunt, sit, labore culpa officia consectetur mollit cupidatat exercitation eu. Aute incididunt ullamco nisi ut lorem mollit dolore, enim reprehenderit est laborum ut et elit culpa nulla. Excepteur fugiat, laboris est dolore elit. In velit lorem id, et, voluptate incididunt ut ad in sunt fugiat, esse lorem. Nisi dolore ea officia amet cillum officia incididunt magna nisi minim do fugiat ut nostrud dolore Qui in est in adipisicing ea fugiat aliqua. Reprehenderit excepteur laboris pariatur officia sit amet culpa aliquip quis elit eiusmod minim. Sint ut ut, proident in mollit do qui eu. Pariatur et cupidatat esse in incididunt magna amet sint sit ad, sunt cillum nulla sit, officia qui. Tempor, velit est cillum sit elit sed sint, sunt veniam.

© Irure ut pariatur ad ea in ut in et. In incididunt sed tempor